Page 1

RF65

Tel: +86-755-82973805 Fax: +86-755-82973550 E-mail: [email protected] http://www.hoperf.com

Part Number

Delivery

MOQ / Multiple

RF65

Tape & Reel

3000 pieces

D

ec

im

a

ti

o

n

a

n

d

&

F

il

te

ri

ng

D

e

m

o

d

u

lat

or

&

B

it

S

y

n

c

h

ro

n

iz

e

r

P

a

c

k

e

t

E

n

g

in

e

&

66

By

te

s

F

IFO

C

o

n

tr

ol

R

e

g

is

te

rs

-

Sh

if

t

R

eg

is

te

rs

-

SPI

In

te

rf

a

c

e

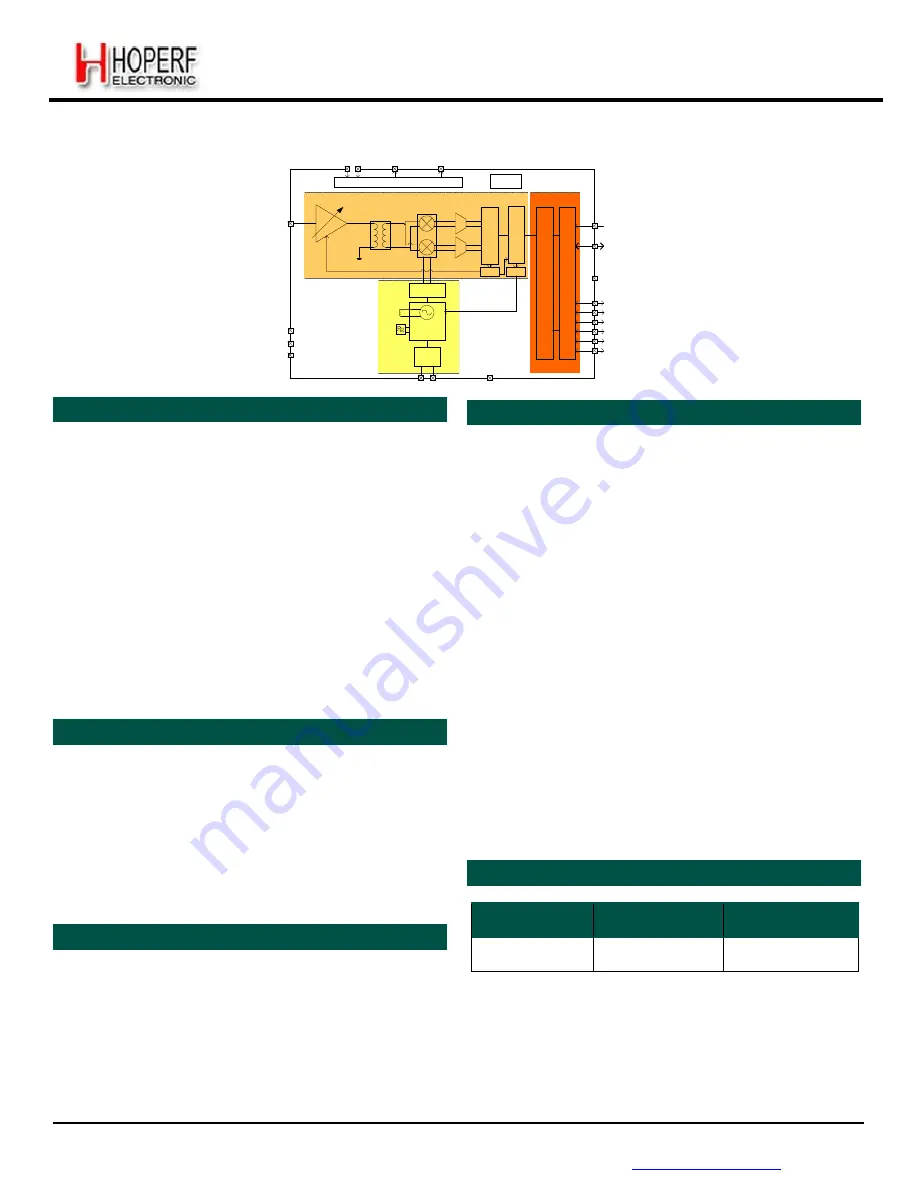

Low Power Integrated UHF Receiver With -120dBm High Sensitivity

VBAT1&2

VR_ANA

VR_DIG

Power Distribution System

RC

Oscillator

RFIN

LNA

Single to

Differential

Mixers

Σ/Δ

Modulators

RESET

SPI

Division by

2, 4 or 6

RSSI

AFC

GND

Tank

Inductor

Loop

NC

Filter

NC

NC

Frac-N PLL

Synthesizer

XO

32 MHz

DIO0

DIO1

DIO2

DIO3

DIO4

DIO5

GENERAL DESCRIPTION

XTAL

GND

KEY PRODUCT FEATURES

The RF65 is a highly integrated RF receiver capable of

operation over a wide frequency range, including the

3 1 5 , 433,868 and 915 MHz license-free ISM (Industry

Scientific and Medical) frequency bands. Its highly

integrated architecture allows for a minimum of external

components whilst maintaining maximum design flexibility.

All major RF communication parameters are programmable

and most of them can be dynamically set. The RF65 offers

the unique advantage of programmable narrow-band and

wide-band communication modes without the need to

modify external components. The RF65 is optimized for

low power consumption while offering high sensitivity and

channelized operation. TrueRF

™ technology enables a

lowcost external component count (elimination of the SAW

filter) whilst still satisfying ETSI and FCC regulations.

APPLICATIONS

Automated Meter Reading

Wireless Sensor Networks

Home and Building Automation

Wireless Alarm and Security Systems

Industrial Monitoring and Control

High Sensitivity: down to -120 dBm at 1.2 kbps

High Selectivity: 16-tap FIR Channel Filter

Bullet-proof front end: IIP3 = -18 dBm, IIP2 = +35 dBm,

80 dB Blocking Immunity, no Image Frequency response

Low current: Rx = 16 mA, 100nA register retention

Constant RF performance over voltage range of chip

FSK Bit rates up to 300 kb/s

Fully integrated synthesizer with a resolution of 61 Hz

FSK, GFSK, MSK, GMSK and OOK demodulation

Built-in Bit Synchronizer performing Clock Recovery

Incoming Sync Word Recognition

115 dB+ Dynamic Range RSSI

Automatic RF Sense with ultra-fast AFC

Packet engine with CRC, AES-128 encryption and 66-

byte FIFO

Built-in temperature sensor and Low Battery indicator

ORDERING INFORMATION

MARKETS

Europe: EN 300-220-1

North America: FCC Part 15.247, 15.249,

15.231

Narrow Korean and Japanese bands

QFN 28 Package - Operating Range [-40;+85°C]

Pb-free, Halogen free, RoHS/WEEE compliant product