6

DW3

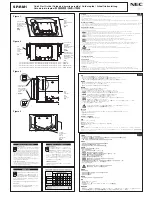

Power system block diagram

Digital

Audio Amp.

Sub

MICRO

Terminal PWB

Main-Digital PWB

+3.3V

DC-DC

Buffer

LED PWB

IR-receiver

LED

Swivel

Motor

Driver

IR-Blaster

Driver

OPT

Output

PLD

(Nereid)

+3.0V

Reg.

VCXO PLL

+2.5V

Reg.

FAN

Vari.

Reg.

+12V

Reg.

+9V

Reg.

LPF

+3.3V

Reg.

+3.3V

Reg.

Audio

ADC

+5V

Reg.

Swivel

Stand

FAN

SD PWB

I

2

C

Buffer

SD

MMC

+3.3V

Reg.

Clock

Buffer

AV-Control

I

2

C

Level

shift

+9V

Reg.

AV SW

+5V

Reg.

+2.5V

Reg.

+1.5V

Reg.

+3.3V

Reg.

Seine2-A

+5V

Reg.

AGC

OOB

+5V

Reg.

+30V

Reg.

+5V

Reg.

Tuner

+1.0V

DC-DC

+1.8V

Reg.

Demodulator

+3.3V

Reg.

+1.05V

DC-DC

FC8

+1.8V

DC-DC

FC8-

DDR2

FC8 PWB

+1.05V

Reg.

+3.3V

Reg.

LVDS

SW

+1.8V

Reg.

Vari.

Reg.

POD-

Vpp

+3.3V

DC-DC

POD-

Vcc

POD PWB

+2.5V

Reg.

+1.2V

Reg.

+3.3V

Reg.

Oberon2

+9V

Reg.

Buffer

+3.3V

Reg.

Key

ROM

Cable

Equalizer

+3.3V

Reg.

+5V

Reg.

Bus

SW

+1.8V

DC-DC

Seine2-D

+2.5V

Reg.

+1.3V

Reg.

+1.3V

DC-DC

Seine2-D

DDR2

+9V

Reg.

Audio

DSP

Audio

PWM

+3.3V

Reg.

Audio

DAC

+5V

Reg.

IR

Mod.

Flash Memory

(OneNand)

Filter PWB

AC120V

AC

SW

+5.6V

STBY+5V

+15V

Vcc

Va

Vs

+10.5V

Power Supply Unit

PDP Panel Module

+16V

Bus

SW

Control PWB

Buffer

x2 x2

x2 x2

P50X901, P50V701 only.