2-1

2. Reference Information

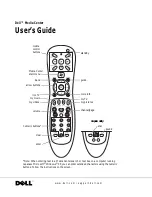

2-1 IC Dsecriptions

2-1-1 AIC1 (AK4393 ; Digital-to-Analog Converter)

Serial

Input

Interface

De-emphasis

Control

De-emphasis

Soft Mute

De-emphasis

Soft Mute

Left Channel

Right Channel

8X

Interpolator

8X

Interpolator

Multi-bit ˘•

Modulator

Multi-bit ˘•

Modulator

Switched

Capacitor Filter

Switched

Capacitor Filter

Control

Register

Double

Speed Select

Soft Mute

Power Down

Serial Data

Bit Clock

Left/Right Clock

Serial

Input Control

Clock Divider

Master Clock

Clock Control

Left Output -

Left

Right Output -

Right

DVSS

DVDD

MCLK

PD

BICK

SDATA

LRCK

SMUTE

DFS

DEM0

DEM1

DIF0

1

2

3

4

5

6

7

8

9

10

11

12

DIF1

13

DIF2

CKS2

CKS1

CKS0

P/S

VCOM

AOUTL+

AOUTL-

AOUTR+

AOUTR-

AVSS

AVDD

VREFH

VREFL

BVSS

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

No.

Pin Name

I/O

Pin Function and Description

1

DVSS

-

Digital Ground. Digital ground is 0V.

2

DVDD

-

Digital Supply. 3.3V or 5.0V nominal.

3

MCLK

I

Master Clock Input.

4

PD

I

Power-down and Reset.

When low the AK4393 is in Power-down Mode and held in reset.

The AK4393 should always be reset after power-up.

5

BICK

I

Audio Serial Data Clock Input.

A clock input of 64fs or more is recommended.

6

SDATA

I

Serial Data Input.

7

LRCK

I

Left/Right Clock Input. Defines the sampling rate, F

s

.

8

SMUTE

(or CS)

I

Soft Mute Input or Chip Select Input.

If the P/S

pin (pin 25) is high, SMUTE controls the

soft mute function as follows:

- When SMUTE goes high, the soft mute cycle is initiated.

- When SMUTE goes low, the output mute is slowly released.

If the P/S pin is low, SMUTE is the Chip Select Input for the Serial Control Mode. Chip

select is active when SMUTE is low.

9

DFS

I

Double Sampling Speed Input.

When low, this pin defines the Normal Speed Mode, and

128 x F

s

oversampling is implemented. When high, the DFS pin defines the Double Speed

Mode, implemented with 64 x F

s

oversampling. This pin features an internal pull-down.

10

DEM0

(or CCLK)

I

De-emphasis Enable #0 or Control Data Clock Input. If the P/S pin (pin 25) is high,

DEM0 is used to select the De-emphasis Mode according to Table 3. If the P/S pin os low

DEM0 is the clock input for the Serial Control Mode.

11

DEM1

(or CDTI)

I

De-emphasis Enable #1 or Control Data Input.

If the P/S

pin (pin 25) is high, DEM1 is

used to select the De-emphasis Mode according to Table 3. If the P/S pin is low, DEM1 is

the control data input for the Serial Control Mode.

12

DIF0

I

Digital Input Format Select #0.

13

DIF1

I

Digital Input Format Select #1.

14

DIF2

I

Digital Input Format Select #2.

15

BVSS

-

Substrate Ground Pin. Substrate ground is 0V.

16

VREFL

I

Low Level Voltage Reference Input.

Normally connected to analog ground.

17

VREFH

I

High Level Voltage Reference Input.

Normally connected to analog supply.

18

AVDD

-

Analog Supply. Analog supply is 5V nominal.

19

AVSS

-

Analog Ground. Analog ground is 0V.

20

AOUTR-

O

Right Channel Negative Output.

21

AOUTR+

O

Right Channel Positive Output.

22

AOUTL-

O

Left Channel Negative Output.

23

AOUTL+

O

Left Channel Positive Output.

24

VCOM

O

Common Voltage Output. Common voltage output is 2.6V nominal.

25

P/S

I

Parallel/Serial Control Mode Select Input.

If Low, the Serial Control Mode is

implemented. If High, the Parallel Control Mode is selected. This pin has an internal

pull-up.

26

CKS0

I

Master Clock Select #0.

27

CKS1

I

Master Clock Select #1.

28

CKS2

I

Master Clock Select #2.

Summary of Contents for DV-P303U

Page 29: ...Reference Information 2 22 MEMO ...

Page 31: ...Product Specification 3 2 MEMO ...

Page 49: ...5 14 Disassembly and Reaasembly MEMO ...

Page 69: ...Circuit Descriptions 6 20 MEMO ...

Page 79: ...Troubleshooting 7 10 MEMO ...

Page 80: ...8 1 8 Exploded View 8 1 Cabinet Assembly 8 2 Deck Assembly Page 8 2 8 3 ...

Page 82: ...8 3 Exploded Views 8 2 Deck Assembly 107 906 ...

Page 83: ...Exploded Views 8 4 MEMO ...

Page 85: ...9 2 Replacement Parts List MEMO ...

Page 87: ...PCB Diagrams 1 11 1 Main COMPONENT SOLDER SIDE ...

Page 88: ...PCB Diagrams 2 11 2 Jack ...

Page 89: ...PCB Diagrams 3 11 3 Key 11 4 Deck ...

Page 90: ...12 1 12 Wiring Diagram ...

Page 91: ...Wiring Diagram 12 2 MEMO ...

Page 93: ...Schematic Diagrams 13 2 13 1 Power ...

Page 94: ...Schematic Diagrams 13 3 13 2 Main Micom ...

Page 95: ...Schematic Diagrams 13 4 13 3 Servo ...

Page 96: ...Schematic Diagrams 13 5 13 4 Video ...

Page 97: ...Schematic Diagrams 13 6 13 5 Audio ...

Page 98: ...Schematic Diagrams 13 7 13 6 RF ...

Page 99: ...Schematic Diagrams 13 8 13 7 ZiVA ...

Page 100: ...Schematic Diagrams 13 9 13 8 DSP ...

Page 101: ...Schematic Diagrams 13 10 13 9 Front Micom VFD Display ...

Page 102: ...Schematic Diagrams 13 11 13 10 Key ...

Page 103: ...Schematic Diagrams 13 12 13 11 Deck ...

Page 104: ...Schematic Diagrams 13 13 13 12 Remote Control ...

Page 105: ...Schematic Diagrams 13 14 MEMO ...