118

CHAPTER 7 DETAILED EXECUTION INSTRUCTIONS

7.32

BTSTL (Test Lower 4 Bits of Byte Data in Memory)

Takes the logical AND of the 4-bit immediate data and the lower 4 bits of byte data at

memory address "Ri", places the results in the condition code register (CCR).

■

BTSTL (Test Lower 4 Bits of Byte Data in Memory)

Assembler format:

BTSTL #u4, @Ri

Operation:

u4 and (Ri) [Test uses lower 4 bits only]

Flag change:

N:

Cleared

Z:

Set when the operation result is "0", cleared otherwise.

V and C: Unchanged

Execution cycles:

2+a cycles

Instruction format:

Example:

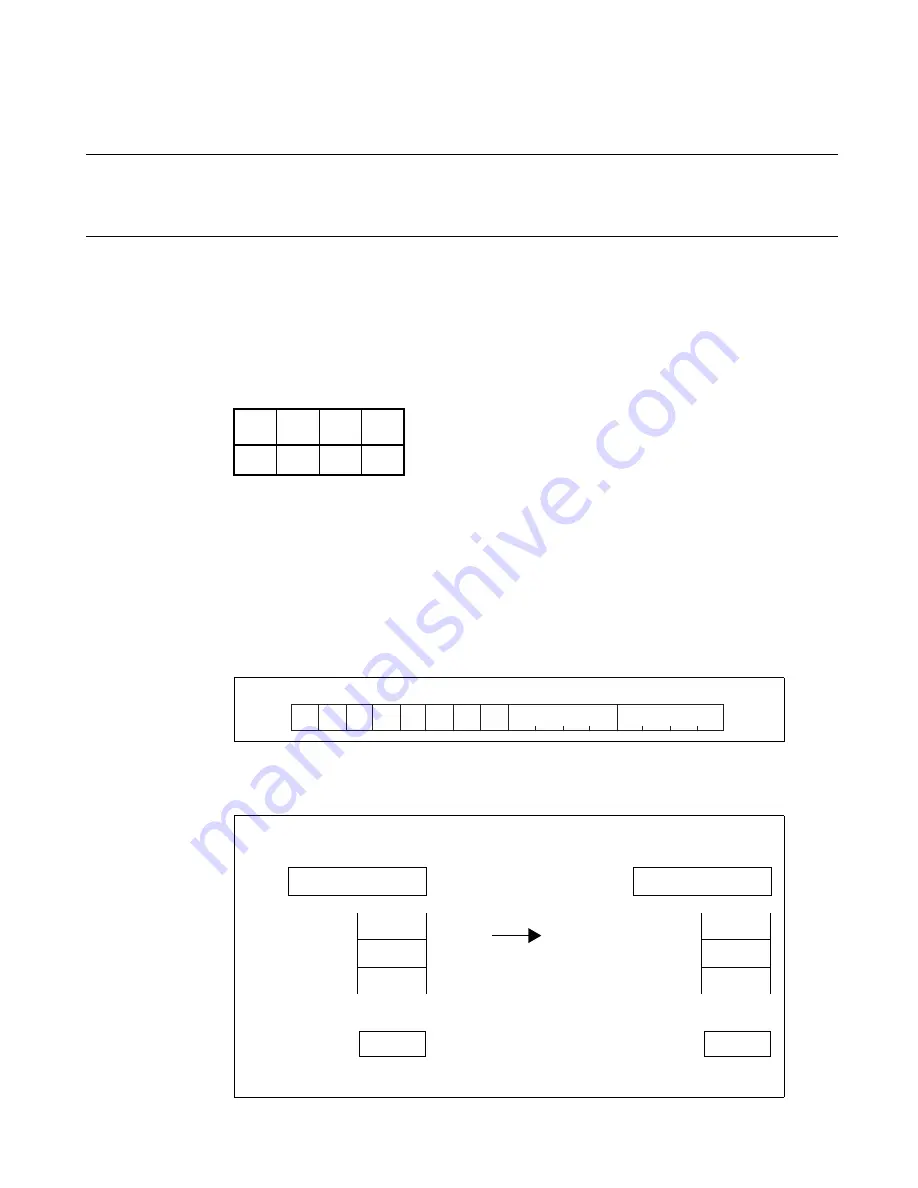

BTSTL #1, @R3

N

Z

V

C

0

C

–

–

MSB

LSB

1

0

0

0

1

0

0

0

u4

Ri

12345678

12345679

1 2 3 4

5 6 7 8

N Z V C

CCR

R3

R3

CCR

0 0 0 0

1 0

N Z V C

0 1 0 0

1 2 3 4

5 6 7 8

12345678

12345679

1 0

Instruction bit pattern :

1000 1000 0001 0011

Before execution

After execution

Memory

Memory

Summary of Contents for FR Family

Page 2: ......

Page 3: ...FUJITSU LIMITED FR Family 32 BIT MICROCONTROLLER INSTRUCTION MANUAL ...

Page 4: ......

Page 8: ...iv ...

Page 14: ...x ...

Page 36: ...12 CHAPTER 2 MEMORY ARCHITECTURE ...

Page 284: ...260 CHAPTER 7 DETAILED EXECUTION INSTRUCTIONS ...

Page 301: ...277 INDEX INDEX The index follows on the next page This is listed in alphabetical order ...

Page 314: ......