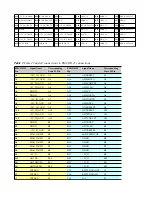

The Table below shows the offset of each of the 16 channels.

MCOR Channel Registers

Channel Base

0x0000

Channel 0

0x0040

Channel 1

0x0080

Channel 2

0x00C0

Channel 3

0x0100

Channel 4

0x0140

Channel 5

0x0180

Channel 6

0x01C0

Channel 7

0x0200

Channel 8

0x0240

Channel 9

0x0280

Channel 10

0x02C0

Channel 11

0x0300

Channel 12

0x0340

Channel 13

0x0380

Channel 14

0x03C0

Channel 15

The Tables below shows how each channel is configured.

Channel Settings Registers

Offset

Reg

0x00

0

Set Point Requested. The Channel

will not respond to setpoint

commands unless the configure bit is

set.

Int32 in uA

0x04

1

Current Set Point

0x08

2

Monitor ADC Reading

0x0C

3

Monitor Average ADC Reading

0x10

4

Monitor Ripple Measurement

0x14

5

FeedBack ADC Reading

0x18

6

FeedBack Average ADC Reading

0x1C

7

FeedBack Ripple Measurement

0x20

8

Fullscale DAC SetPoint Current

0x24

9

Fullscale Monitor ADC ReadBack

Current

0x28

A

Ramp Rate

Int32 uA/sec

0x2C

B

Samples per Average

UInt32

0x30

C

Configuration/Status Register

0x34

D

Set Configuration Register

0x38

E

Reset Configuration Register

0x3C

F

Fullscale FeedBack ADC ReadBack

Current