14. How to use

RX4111CE

Jump to

ETM62E-02

Seiko Epson Corporation

27

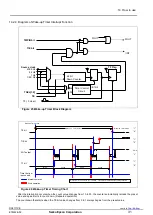

14.2. Wake-up Timer Interrupt Function

The Wake-up timer interrupt function generates an interrupt event periodically at any Wake-up set between 244.14

s

and 31.9 years. It can be paused and can also be used as an accumulate timer.

tRTN2 after the interrupt occurs, the /INT status is automatically released (/INT status changes from

low-level to Hi-z).

14.2.1. Related Registers For Function Of Wake-up Timer Interrupt Function

Table 19 Wake-up Timer Interrupt Register

Bank1

Address

[h]

Function

bit 7

bit 6

bit 5

bit 4

bit 3

bit 2

bit 1

bit 0

A

Timer Counter 0

128

64

32

16

8

4

2

1

B

Timer Counter 1

32768

16384

8192

4096

2048

1024

512

256

C

Timer Counter 2

8388608 4194304

2097152 1048576 524288 262144 131072

65536

D

Extension Register

FSEL1

FSEL0

USEL

TE

WADA

▲

TSEL1

TSEL0

E

Flag Register

POR

z

UF

TF

AF

EVF

VLF

XST

F

Control Register

z

z

UIE

TIE

AIE

EIE

z

STOP

Bank2-D

Timer Control

z

z

z

z

TBKON

TBKE

TMPIN

TSTP

Before setting the operation, clear the TE bit to 0.

When the Wake-up timer function is not being used, the Wake-up Timer Counter0,1 register can be used as a

RAM register. In such cases, stop the Wake-up timer function by writing 0 to the TE and TIE bits.

1) Down counter for Wake-up timer

(

Timer Counter

2, 1, 0

)

This register is used to set the default (preset) value for the counter. Any count value from 1

to 16777216

can be set.

Be sure to write 0 to the TE bit before writing the preset value.

When TE=0, read out data of timer counter is default (Preset) value. When TE = 1, read out data of timer counter is

just counting value. But, when access to timer counter data, counting value is not held.

Therefore, for example, perform twice read access to obtain right data, and a way to adopt the case that two data

accorded is necessary.

2) TSEL1, TSEL0 bit

The combination of these three bits is used to set the countdown period (source clock) for this function.

Table 20 TSEL bit Source Clock Select

TSEL1

(bit 1)

TSEL0

(bit 0)

Source clock

Auto release time

tRTN2 Min.

0

0

4096

Hz

/Once per 244.14

s

122

s

0

1

64

Hz

/Once per 15.625 ms

7.813

ms

1

0

1

Hz

/Once per second

7.813

ms

1

1

1/60

Hz

/Once per minute

7.813

ms

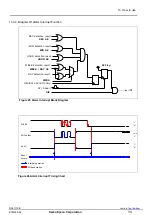

1) The /INT pin's Auto reset time (tRTN2) varies as shown above according to the source clock setting.

2)

The first countdown shortens than a source clock.

When selected 4096 Hz / 64 Hz / 1 Hz as a source clock, one period of error occurs at the maximum.

When selected 1/60 Hz, 1 Hz of error occurs at the maximum.

The example of the error of the first countdown: A preset value is 04h.

Cycle error

初回周期誤差

TE

Designated cycle

Internal source clock

TF Flag

”0”

⇒

“1”

TF

3

2

1

4

Down counter

4

Figure 20 Wake-up Timer Initial Sequence (cycle error)