13. Overview of Functions and Registers

RX4111CE

Jump to

ETM62E-02

Seiko Epson Corporation

24

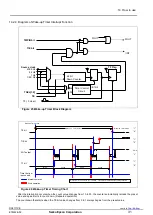

13.3.5. Power Switching Circuit-Related Register

Bank3 02h

1) INIEN bit

This bit sets power switching operation and SPI-Bus communication stop at backup

2) SMPT1, SMPT0 bit

This bit sets the intermittent operation active time of the voltage monitoring circuit of the built-in MOS switch.

3) SWSEL1, SWSEL0 bit

When not using the power switching function, this bit sets the built-in MOS switch.

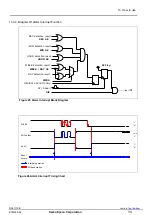

13.3.6. Time stamp-related register

Please refer to [13.8. Time stamp function] for the details.

1) Time stamp and status record register (Bank2 - 0h

9h; Bank4, 5, 6, 7 - 0h

Fh)

This register records time stamp data from 1/1000 second digit to Year digit and internal state

when an event occurs.

2) Command trigger Time stamp control register (Bank2 - Eh

Fh)

This register is used when triggering time stamp using SPI-Bus communication access.

3) Time stamp trigger control register (Bank3 - 5h)

This register is used to perform time stamp trigger.

13.3.7. RAM registers

(Bank4, 5, 6, 7)

This RAM register is read/write accessible for any data in the range from 0h to Fh.