14

QUICK START

If you use TINALab Spartan board together with TINA circuit simulation software and

TINALab II High Speed Multifunction PC Instrument there is possible to develop VHDL code

with simulation capabilities and after implementing, you can download your design and measure

back the signals with the help of TINALab II Digital Signal Generator and Logic Analyzer. TINA

provides code developing, simulation and measurement control with TINALab II, which does

power supplies and signal link.

To generate FPGA downloadable configuration file, you will need Xilinx ISE

Webpack

TM

software

(

http://www.xilinx.com/ise/logic_design_prod/webpack.htm

).

The following examples apply TINA 8 and Xilinx ISE

Webpack

TM

10.1.02.

1.

Connect TINALab II with your XC2S FPGA card as described under TINALab II User

Port on page 7.

2.

Open the \examples\vhdl\fpga\full_add.tsc sample design.

3.

Press the VHD button on the toolbar to enter interactive mode.

4.

Toggle the switches to change the logic low and high levels on the input of the adder.

Depending on the state of the inputs the outputs change state as the function of the full

adder.

5.

Now, create the VHDL program source for the FPGA card.

Press T&M > Create VHD & UCF file… Save the vhd and ucf file.

6.

Start Xilinx ISE

WebPACK

TM

and create a new project (File > New project…) with the

following settings.

Project name: Full_Add

Project location: [Setting Folder]\VHDL\Projects2\e_FULL_ADD_entity (See Settings

Folder value View > Editor Options > Environment Variables.)

Top-level source type: HDL

Click Next.

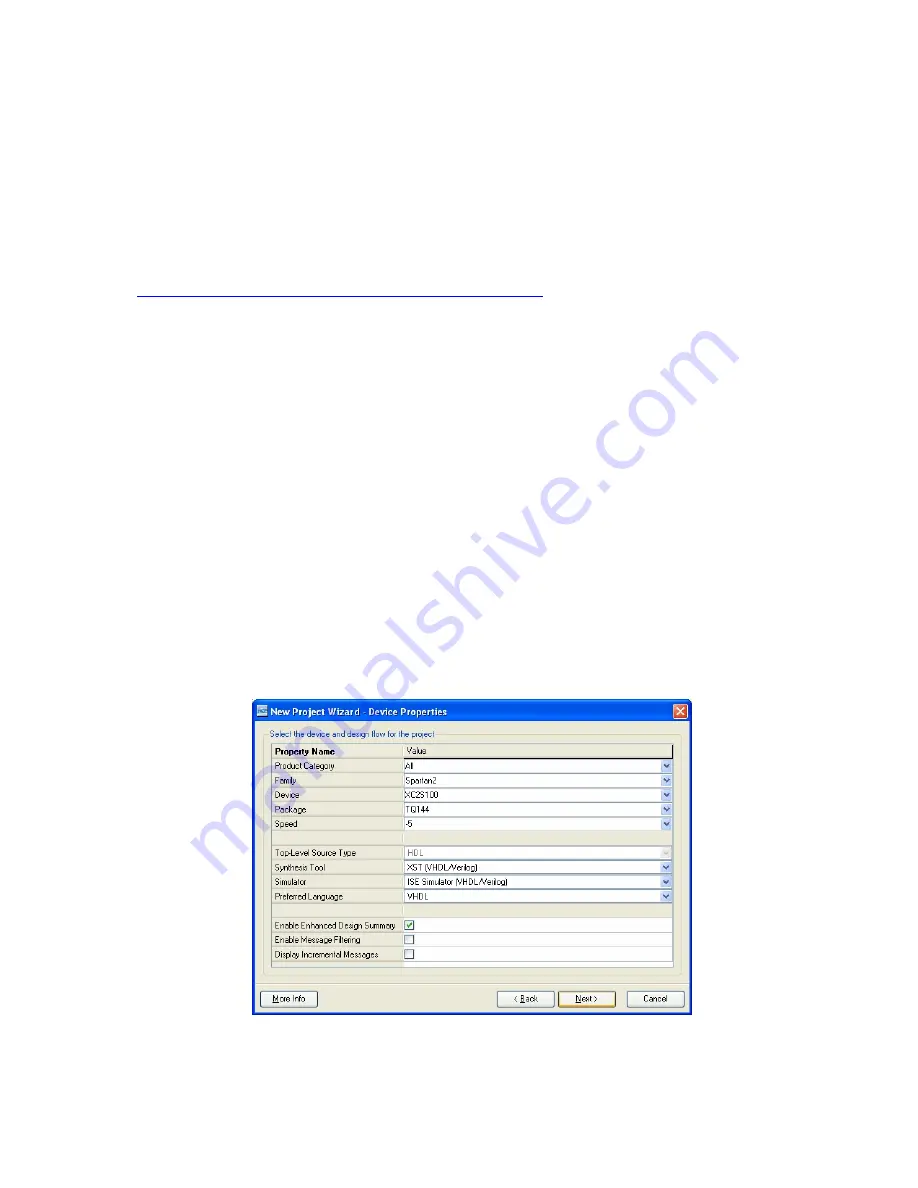

7.

Fill the Device Properties dialog. Note, - that Device should exactly match the FPGA type

mounted on the board.

Click Next then Next again to skip the “Add New Source” window.