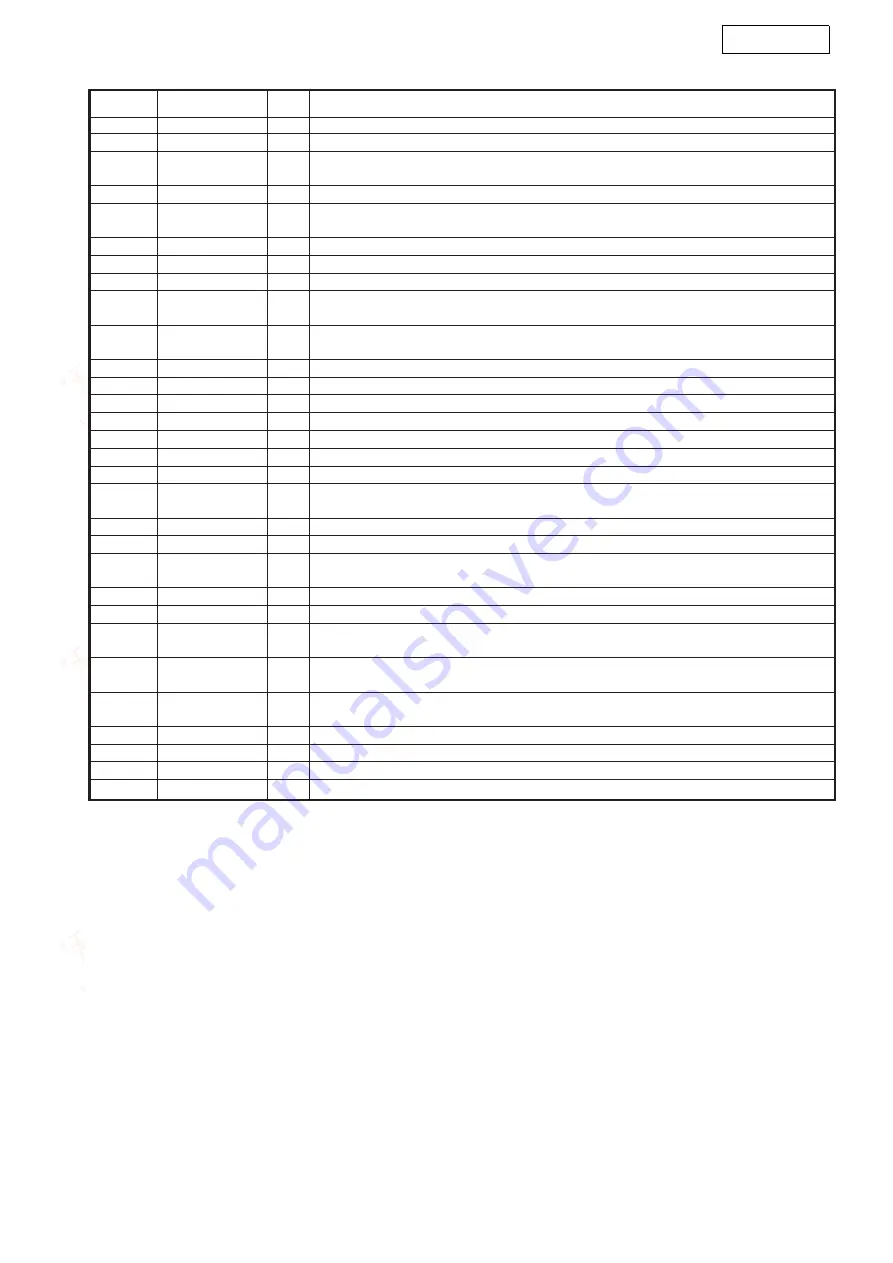

12

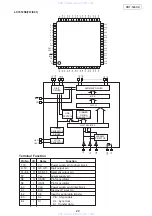

DHT-500SD

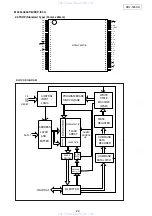

Description

Pin No.

Pin Name

Type

43

CE

O

Center Error Signal Output. Center error output reference to VCI

34

NEVO

O

SIGO Bottom Envelope Output. Bottom envelope for mirror detection

37

DFT

O

Defect Output. Pseudo CMOS output. When a defect is detected, the DFT output goes high. Also

the servo AGC output can be monitored at this pin, when CAR bits 7-4 are ‘0011’

29

MIRR

O

Mirror Detect Output. Mirror Detect comparator output. Pseudo CMOS output

36

PI

O

Pull-in Signal Output. The summing signal output of A, B, C, D or PD1, PD2 for mirror detection.

Reference to VCI

22

DVDLD

O

APC output. DVD APC output pin to control the laser power

24

CDLD

O

APC output. CD APC output pin to control the laser power

56

BYP

I/O

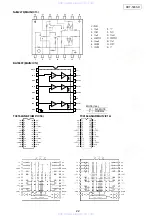

The RF AGC integration capacitor CBYP, is connected between BYP and VPA

9

CP

I/O

Differential Phase tracking LPF pin. An external capacitance is connected between this pin and

the CN pin

10

CN

I/O

Differential Phase tracking LPF pin. An external capacitance is connected between this pin and

the CP pin

45

LCP

—

Center Error LPF pin. An external capacitance is connected between this pin and the LCN pin

44

LCN

—

Center Error LPF pin. An external capacitance is connected between this pin and the LCP pin

30

MP

—

MIRR signal Peak hold pin. An external capacitance is connected to between this pin and VPB

31

MB

—

MIRR signal Bottom hold pin. An external capacitance is connected to between this pin and VPB

39

MEV

—

Sigo Bottom Envelope pin. An external capacitance is connected to between this pin and VPB

17

CDTE

—

CD Tracking. E-F Opamp output for feedback

38

TPH

—

PI Top Hold pin. An external capacitance is connected to between this pin and VPB

26

VC

—

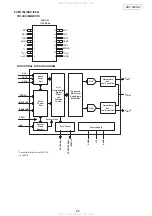

Reference Voltage output. This pin provides the internal DC bias reference voltage (+2.5V lix).

Output Impedance is less than 50ohms

27

VCI

—

Reference Voltage input. DC bias voltage input for the servo input reference

18

VCI2

—

Reference Voltage input. DC bias voltage input for the servo input reference

55

RX

—

Reference Resistor Input. An external 8.2kohm, 1% resistor is connected from this pin to ground

to establish a precise PTAT (proportional to absolute temperature) reference current for the filter

33

MLPF

—

MIRR signal LPF pin. An external capacitance is connected between this pin and VPB

19

NC

—

No Connect

48

SDEN

I

Serial Data Enable. Serial Enable CMOS input. A high level input enable the serial port (Not to be

left open)

47

SDATA

I/O

Serial Data. Serial data bi-directional CMOS pin. NRZ programming data for the internal registers

is applied to this input ( Not to be left open)

46

SCLK

I

Serial Clock. Serial Clock CMOS input. The clock applied to this pin is synchronized with the data

applied to SDATA (Not to be left open)

58

VPA

Power. Power supply pin for the RF block and serial port

28

VPB

Power. Power supply pin for the servo block

50

VNA

Ground. Ground pin for the RF block and serial port

20

VNB

Ground. Ground pin for the servo bolck

www. xiaoyu163. com

QQ 376315150

9

9

2

8

9

4

2

9

8

TEL 13942296513

9

9

2

8

9

4

2

9

8

0

5

1

5

1

3

6

7

3

Q

Q

TEL 13942296513 QQ 376315150 892498299

TEL 13942296513 QQ 376315150 892498299