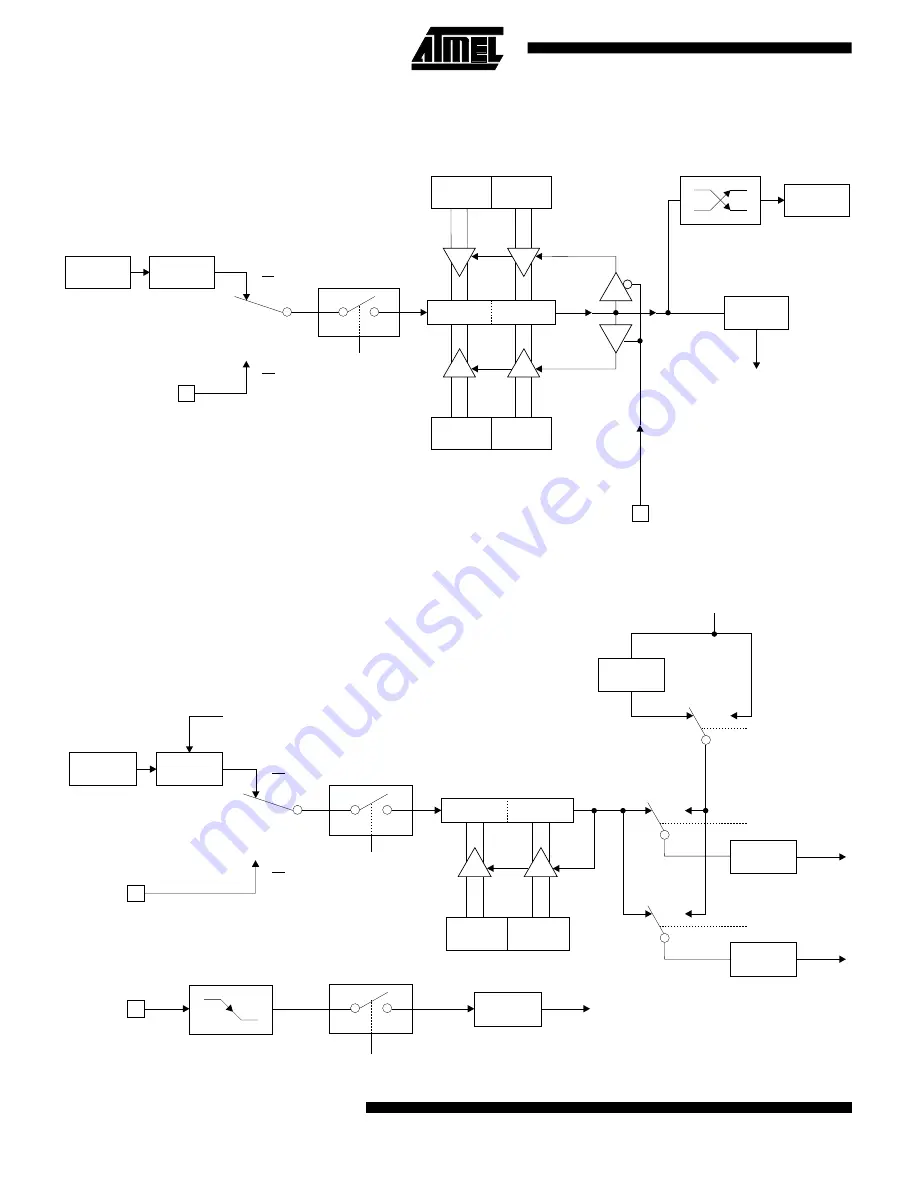

OSC

EXF2

TF2

T2EX PIN

COUNT

DIRECTION

1=UP

0=DOWN

T2 PIN

TR2

CONTROL

OVERFLOW

(DOWN COUNTING RELOAD VALUE)

(UP COUNTING RELOAD VALUE)

TOGGLE

TIMER 2

INTERRUPT

12

RCAP2L

RCAP2H

0FFH

0FFH

TH2

TL2

C/T2 = 0

C/T2 = 1

÷

Figure 3. Timer 2 Auto Reload Mode (DCEN = 1)

OSC

SMOD1

RCLK

TCLK

Rx

CLOCK

Tx

CLOCK

T2EX PIN

T2 PIN

TR2

CONTROL

"1"

"1"

"1"

"0"

"0"

"0"

TIMER 1 OVERFLOW

NOTE: OSC. FREQ. IS DIVIDED BY 2, NOT 12

TIMER 2

INTERRUPT

2

2

6

16

RCAP2L

RCAP2H

TH2

TL2

C/T2 = 0

C/T2 = 1

EXF2

CONTROL

TRANSITION

DETECTOR

EXEN2

÷

÷

÷

÷

Figure 4. Timer 2 in Baud Rate Generator Mode

8

AT89C52