Evaluation Board User Guide

UG-076

Rev. A | Page 5 of 16

QUICK START GUIDE TO THE

When the evaluation software is installed, the evaluation board

is connected, and the software is loaded, use the following steps

to configure and lock the PLL. These steps assume that the input

signal is present, the evaluation board has not been modified,

and that the PLL loop filter is suitable for the user’s application.

This quick start guide covers only simple PLL operation to start

the PLL. See the

data sheet and Evaluation Software

Components section for a detailed explanation of the various

features.

The following case is an example for the

using the

values in Table 1.

Table 1. Default Parameter Values

Parameter Value

Input Frequency

19.44 MHz on REF1

Output Frequency

148.5 MHz

Reference Divider

72

Phase Detector Frequency

270 kHz

Feedback Divider

5500

VCO Frequency

1485 MHz

VCO Divider

2

Channel Divider

5

1.

Turn the PLL on by selecting

Normal Op

from the

PLL

MODE

box found at the top of the main window (see

2.

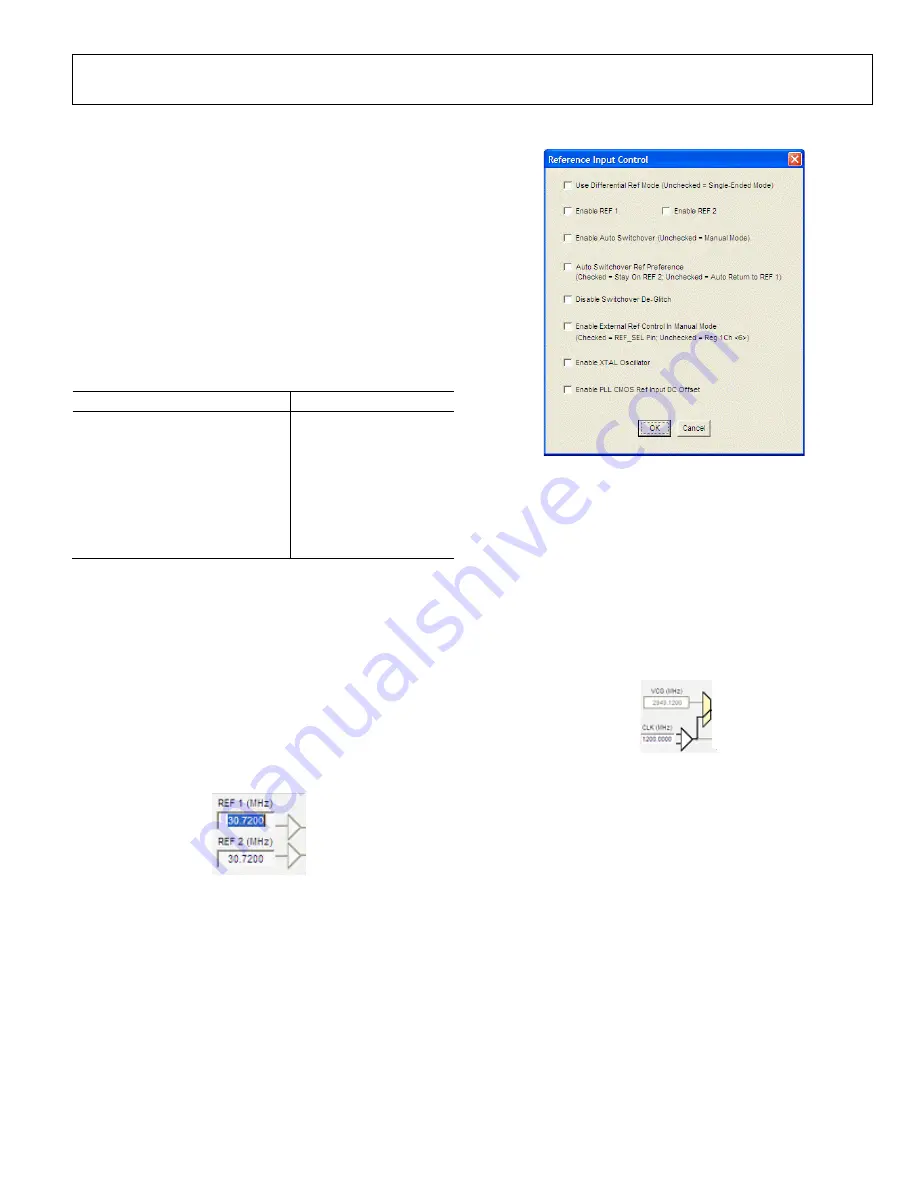

Enter the intended reference input frequency (in

megahertz) in the

REF 1 (MHz)

box at the upper left

corner of the main window.

3.

Click the triangular buffer symbol immediately to the

right of the input reference frequency text boxes (see

Figure 4) to open the

Reference Input Control

window

shown in Figure 5. Turn the REF1 reference input buffer on

by selecting the

Enable REF 1

check box, and then click

OK

.

0

874

6-

024

Figure 4. Buffer Symbol

08

74

6-

0

04

Figure 5.

Reference Input Control

Window

4.

When the window closes, the

WRITE

button under the

REGISTER W/R

section in Figure 8 blinks red. This

indicates that there are settings that have not been loaded

to the

evaluation board. Click the blinking red

WRITE

button to load these settings to the evaluation

board.

5.

Select the VCO as the input to the clock distribution

circuitry by clicking the mux symbol that is located

immediately to the right of the

VCO (MHz)

box (see

0

874

6-

025

Figure 6. Mux Symbol

6.

When the VCO is selected, the border of the

VCO (MHz)

box changes from gray to black. The current VCO

frequency is shown in the

VCO (MHz)

box.