CoreModule 420

Reference Manual

1

Chapter 1

About This Manual

Purpose of this Manual

This manual is for designers of systems based on the CoreModule™ 420 PC/104 single board computer

(SBC) module. This manual contains information that permits designers to create an embedded system

based on specific design requirements.

Information provided

in this reference manual includes:

•

CoreModule 420 SBC Specifications

•

Environmental requirements

•

Major chips and features implemented

•

CoreModule 420 SBC connector/pin numbers and definition

•

BIOS Setup information

Information not provided

in this reference manual includes:

•

Detailed chip specifications

•

Internal component operation

•

Internal registers or signal operations

•

Bus or signal timing for industry standard busses and signals

Reference Material

The following list of reference materials may be helpful for you to complete your custom design

successfully. Most of this reference material is also available on the Ampro web site in the Embedded

Design Resource Center. The Embedded Design Resource Center was created for embedded system

developers to share Ampro’s knowledge, insight, and expertise gained from years of experience.

Specifications

•

PC/104 Specifications Revision 2.5, November 2003.

For latest revision of the PC/104 specifications, contact the PC/104 Consortium, at:

Web site:

http://www.pc104.org

Chip Specifications

The following chip specifications are used in the CoreModule 420 processor module:

•

STMicroelectronics and the chip, STPC

®

Atlas, used for the embedded CPU

Web site:

http://us.st.com/stonline/books/pdf/docs/7341.pdf

•

Standard Microsystems Corp and the chip, FDC37B782, used for the Super I/O controller

Web site:

http://www.smsc.com/main/catalog/fdc37b78x.html

•

Intel Corporation and the chip, 82551ER, used for the Ethernet controller

Web site:

http://www.intel.com/design/network/products/lan/controllers/82551er.html

Summary of Contents for CoreModule 420

Page 1: ...CoreModule 420 PC 104 Single Board Computer Reference Manual P N 5001692A Revision A ...

Page 6: ...Contents vi Reference Manual CoreModule 420 ...

Page 10: ...Chapter 1 About this Manual 4 Reference Manual CoreModule 420 ...

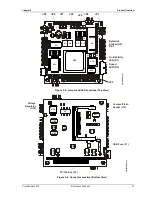

Page 22: ...Chapter 2 Product Overview 16 Reference Manual CoreModule 420 ...

Page 50: ...Chapter 3 Hardware 44 Reference Manual CoreModule 420 ...

Page 64: ...Appendix A Technical Support 58 Reference Manual CoreModule 420 ...

Page 66: ...Appendix B Connector Part Numbers 60 Reference Manual CoreModule 420 ...

Page 70: ...Index 64 Reference Manual CoreModule 420 ...

Page 71: ......

Page 72: ......