ADM-VPX3-9Z2 User Manual

V1.1 - 16th January 2020

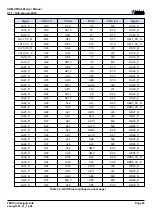

3.5.4 Module to Carrier Global Clocks (CLK_M2C)

A connected FMC+ board can generate a number of differential Global clocks (as per the FMC standard). They

each connect to an global clock input on the FPGA.

Signal

Frequency

FPGA Input

IO Standard

"P" pin

"N" pin

CLK_M2C_0

Variable

Bank 66

LVDS

Y5

AA5

CLK_M2C_1

Variable

Bank 66

LVDS

Y4

Y3

CLK_M2C_2

Variable

Bank 65

LVDS

AF6

AG6

CLK_M2C_3

Variable

Bank 65

LVDS

AE7

AF7

Table 13 : CLK_M2C Connections

3.5.5 Module to Carrier MGTREF Clocks (GBTCLK_M2C)

A connected FMC board can generate a number of differential MGT Reference clocks (as per the FMC standard)

. They each connect to an MGTREFCLK input on the FPGA.

Signal

Frequency

FPGA Input

IO Standard

"P" pin

"N" pin

GBTCLK_0_M2C

Variable

MGTREFCLK_228

LVDS

L8

L7

GBTCLK_1_M2C

Variable

MGTREFCLK_229

LVDS

G8

G7

GBTCLK_2_M2C

Variable

MGTREFCLK_230

LVDS

C8

C7

GBTCLK_3_M2C

Variable

MGTREFCLK_128

LVDS

R27

R28

GBTCLK_4_M2C

Variable

MGTREFCLK_129

LVDS

L27

L28

GBTCLK_5_M2C

Variable

MGTREFCLK_130

LVDS

G27

G28

Table 14 : GCLK_M2C Connections

3.5.6 PS_REFCLK

The PS reference clock is an independent 50.0MHz reference clock. This is the master clock of the PS side of

the MPSoC.

Signal

Frequency

FPGA Input

IO Standard

pin

PS_REFCLK

50MHz

PS_REF_CLK (Bank

503)

LVCMOS18

U24

Table 15 : PS_REFCLK Connection

3.5.7 VIDEO_CLK

An optional independent 27.0MHz reference clock is provided. This can be used to clock the video sections in

the PS side of the MPSoC.

Page 13

Functional Description

ad-ug-1323_v1_1.pdf