5

5

4

4

3

3

2

2

1

1

D

D

C

C

B

B

A

A

JTRST#

JTDI

JTMS

JTCK

JRTCK

JTDO

READY#

DV12

POWE#

POCE0#

POOE0#

RDQ[0..31]

R DQS[0..3]

RDQM[0..3]

RA[0..13]

RCLK0#

R CS#

RRAS#

RCAS#

RWE#

R CKE

RBA[0..1]

RCLK1

RCLK1#

RCLK0

PDA[0..22]

PDD [0..7]

U2TX

U2RX

U1RX

U1TX

U0RX

U0TX

AO1MCLK

AO1LRCK

AO1BCK

ASPDIF

OSCL0

OSDA0

DV25

DV33

RVREF

OXTALI

OXTALO

D VDDKP

FS

CAPVPLL

RV

RE

F

CAPVGND

AVDDRKP

AVDD_APLL0

AVDD_APLL1

AVDDBGKP

AVDD_DMPLL1

AVDD_VPLL

AVDD YKP

AVDD_DMPLL0

APLLCAP1

APLLCAP0

ATP1

ATP2

OPWM0

REQUEST#

ORESET#

VCXO0

TS1CLK

TS1ERROR

TS1SYNC

TS1VALID

TS1DATA[0..7]

VOR[0..7]

VOG[0..7]

VOB[0..7]

VOPCLK

VOHSYNC

VOVSYNC

VODE

AO1SDATA0

U2CTS

OI RI

AUD_CTRL

AVD

D

_

VP

L

L

RA

7

RA

2

RDQ

M

0

JTDO

VOR7

G

R

T

S1

D

AT

A0

PD

A1

AVD

D

Y

K

P

RC

L

K

1

RC

K

E

R

R

AS#

R

C

AS#

RDQ

1

3

VOB4

T

S

1E

RRO

R

PD

A1

8

PD

A1

4

PD

A2

RDQ

M

3

RDQ

1

9

RA

13

RDQ

1

D ONE

OI RI

VOPCLK

VOG7

VOB5

U2CTS

VCXO0

OP

WM

0

T

S1

D

AT

A3

PD

A2

2

OX

T

A

L

O

RDQ

3

0

RDQ

2

0

R

BA0

RDQ

1

0

RC

L

K

0

VOR0

VOG1

AO1BCK

U1RX

U0TX

OSCL0

T

S1

D

AT

A7

T

S1

D

AT

A4

PD

A9

AVD

D

_

AP

L

L

1

RA

6

VOR6

PD

A0

A

V

DDB

G

K

P

RDQ

M

2

RA

11

RDQ

6

JRTCK

VOB3

ASPDIF

OSDA0

P

DD3

T

S1

D

AT

A1

PD

A1

7

AVD

D

_

AP

L

L

0

RDQ

1

8

RA

12

RW

E

#

RDQ

0

VOG6

P

DD0

T

S1

D

AT

A2

PD

A2

1

RDQ

2

9

RDQ

2

5

RA

5

RDQ

9

VODE

VOG0

POCE0#

P

DD1

APL

L

C

A

P

1

T

S1

D

AT

A6

PD

A8

PD

A6

PD

A5

RDQ

2

6

RDQ

2

3

RDQ

1

6

RA

0

RCS

#

VOR5

AO1LRCK

U1TX

RA

9

RA

4

RA

1

RD

Q

S

1

RD

Q

S

0

RDQ

5

VOR1

VOB2

AO1SDATA0

P

DD2

APL

L

C

A

P

0

FS

PD

A1

6

GND

RDQ

1

7

RDQ

1

5

JTCK

JTMS

JTDI

VOR2

VOG5

AO1MCLK

U2RX

VCXO1

PD

A2

0

C

A

PVG

N

D

RDQ

2

8

RDQ

2

4

RDQ

8

RDQ

3

R

C

LK

0#

JTRST#

VOVSYNC

VOB7

T

S1

D

AT

A5

PD

A7

PD

A4

DV

D

D

K

P

RA

10

RDQ

1

2

VOR4

VOG3

P

DD6

T

S

1

VAL

ID

PD

A1

3

A

V

DD_DM

P

L

L

1

OX

TA

L

I

AT

P1

R

C

LK

1#

RA

8

RA

3

RDQ

M

1

RDQ

7

RDQ

4

ORESET#

VOB1

POOE0#

POWE#

P

DD7

P

DD4

T

S

1CLK

A

V

DDRK

P

A

V

DD_DM

P

L

L

0

RDQ

1

4

READY#

REQUEST#

VOG4

C

APVPL

L

B

PD

A1

9

PD

A1

5

RDQ

2

7

RD

Q

S

3

RDQ

2

VOHSYNC

VOB6

AUD_CTRL

U2TX

U0RX

T

S

1

SYN

C

PD

A1

1

PD

A3

AT

P2

RDQ

3

1

RD

Q

S

2

RDQ

2

1

R

BA1

RDQ

1

1

VOR3

VOG2

VOB0

TUNER_SW

P

DD5

PD

A1

2

PD

A1

0

RDQ

2

2

R

B

G

DV33

DV25

DV12

DV33

DV12

JTRST#

8

JTDI

8

JTMS

8

JTCK

8

JRTCK

8

JTDO

8

GND

1,2,3,4,6,7,8

DV12

2,6

POCE0#

8

POOE0#

8

POWE#

8

RDQ[0..31]

7

RDQS[0..3]

7

RDQM[0..3]

7

RA[0..13]

7

RCLK0

7

RCLK0#

7

RCS#

7

RRAS#

7

RCAS#

7

RWE#

7

RCKE

7

RBA[0..1]

7

RCLK1

7

RCLK1#

7

PDA[0..22]

8

PDD[0..7]

8

U2TX

1,8

U2RX

1,8

U1RX

8

U1TX

8

U0RX

1,8

U0TX

1,8

READY#

1

AO1MCLK

1

AO1BCK

1

AO1LRCK

1

AO1SDATA0

1

ASPDIF

1

OPWM0

6

OSCL0

6

OSDA0

6

DV25

2,6,7

DV33

1,2,6,8

RVREF

6

OXTALI

6

OXTALO

6

DVDDKP

6

FS

6

CAPVPLL

6

CAPVGND

6

AVDDRKP

2,6

AVDD_APLL0

2,6

AVDD_APLL1

2,6

AVDDBGKP

2,6

AVDD_DMPLL1

2,6

AVDD_VPLL

2,6

AVDDYKP

2,6

AVDD_DMPLL0

2,6

APLLCAP1

6

APLLCAP0

6

ATP1

6

ATP2

6

REQUEST#

1

ORESET#

1,4,8

VCXO0

6

TS1CLK

4

TS1ERROR

4

TS1SYNC

4

TS1VALID

4

TS1DATA[0..7]

4

VOR[0..7]

1

VOG[0..7]

1

VOB[0..7]

1

VOPCLK

1

VOHSYNC

1,8

VOVSYNC

1,8

VODE

1

U2CTS

6

O IRI

6

AUD_CTRL

1

R

8

B

8

G

8

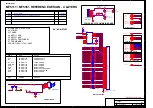

Title

Size

Document Number

R e v

Date:

Sheet

o f

MT5351RA-V2

1

Custom

5

8

Monday, February 20, 2006

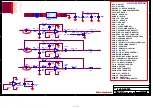

MT5351 ASIC

MediaTek Confidential

TwinSon Chan

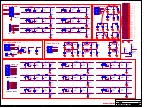

JTAG PORT

GLOBAL SIGNAL

DDR MEMORY

FLASH INTERFACE

UART (RS232)

AUDIO INTERFACE

ANALOG PART

TEST PURPOSE

TS INPUT

DIGITAL VIDEO OUTPUT

Add by Ada

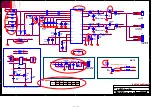

R36

330

R0603/SMD

TP6

TUNER_SW

TP/SMD/D1.0

C118

0.1uF

C0603/SMD

TP5

IR

TP/SMD/D1.0

TP2

IOB_Y5

TP/SMD/D1.0

MT5351

U14

MT5351

BGA471/SMD

P

DCD2#

A1

4

P

D

IOIS

16#

A1

5

PD

A0

B2

4

PD

A1

A2

4

PD

A2

D23

PD

A3

C23

PD

A4

B2

3

PD

A5

A2

3

PD

A6

D22

PD

A7

C22

PD

A8

B2

2

PD

A9

A2

2

PD

A1

0

D21

PD

A1

1

C21

PD

A1

2

B2

1

PD

A1

3

A2

1

PD

A1

4

D20

PD

A1

5

C20

PD

A1

6

B2

0

PD

A1

7

A2

0

PD

A1

8

D19

PD

A1

9

C19

PD

A2

0

B1

9

PD

A2

1

A1

9

PD

A2

2

D18

PD

A2

3

C18

PD

A2

4

B1

8

PD

A2

5

A1

8

P

DCE

1#

D17

P

DCE

2#

C17

PD

O

E#

B1

7

P

D

IO

RD#

A1

7

PD

IO

WR

#

D16

PD

WE#

C16

PD

IR

EQ

#

B1

6

PD

R

ESET

A1

6

PD

WAI

T

#

D15

PD

IN

PAC

K#

C15

P

DRE

G

#

B1

5

PD

EN

PO

D

B1

4

T0

C

L

K

C14

T

0

SYN

C

D14

T

0

VAL

ID

A1

3

T0

D

A

TA

0

B1

3

T0

D

A

TA

1

C13

T0

D

A

TA

2

D13

T0

D

A

TA

3

A1

2

T0

D

A

TA

4

B1

2

T0

D

A

TA

5

C12

T0

D

A

TA

6

D12

T0

D

A

TA

7

A1

1

T1

C

L

K

B1

1

T

1

SYN

C

C11

T

1

VAL

ID

D11

T1

D

A

TA

0

A1

0

T1

D

A

TA

1

B1

0

T1

D

A

TA

2

C10

T1

D

A

TA

3

D10

T1

D

A

TA

4

A9

T1

D

A

TA

5

B9

T1

D

A

TA

6

C9

T1

D

A

TA

7

D9

OP

WM

0

D8

OR

TC

V

D

D

D7

OR

TC

O

B8

OR

TC

I

A8

OP

WM

1

C8

O

R

T

C

VSS

C7

FS

A6

CIN_Y

0

A7

IOR_Y

6

B3

IO

B_

Y5

A3

IOG_

Y

4

C4

IO

X_

Y3

B4

IO

Y_

Y2

A4

IOC_Y

1

C5

C

APVPL

L

D5

APL

L

C

AP1

D4

APL

L

C

AP0

E4

AG

N

D

L11

AG

N

D

L12

AG

N

D

L13

AG

N

D

M1

1

AG

N

D

M1

2

AG

N

D

M1

3

AG

N

D

N11

AG

N

D

N12

AG

N

D

N13

P

DD0

A2

7

P

DD1

B2

6

P

DD2

A2

6

P

DD3

C25

P

DD4

B2

5

P

DD5

A2

5

P

DD6

D24

P

DD7

C24

P

DCD1#

A2

8

CV

DD

M5

CV

DD

N5

CV

DD

U5

CV

DD

E1

0

CV

DD

E1

9

CV

DD

M2

4

CV

DD

N24

CV

DD

U24

CV

DD

AE1

4

CV

DD

AE1

5

IOVDD

P5

IOVDD

R1

IOVDD

R2

IOVDD

R3

IOVDD

R4

IOVDD

R5

IOVDD

T5

IOVDD

E11

IOVDD

E12

IOVDD

E13

IOVDD

E14

IOVDD

E15

IOVDD

E16

IOVDD

E17

IOVDD

E18

IOVDD

P24

IOVDD

R24

IOVDD

R25

IOVDD

R26

IOVDD

R27

IOVDD

R28

IOVDD

T24

POWE#

B27

POCE0#

B28

POOE0#

C26

POCE1#

C27

POOE1#

C28

POCE2#

D25

POOE2#

D26

OSDA0

E1

OSCL0

F4

OSDA1

E3

OSCL1

E2

U0TX

F3

U0RX

F2

U1TX

F1

U1RX

G4

U2TX

G3

U2RX

G2

U2CTS

G1

U2RTS

H4

AO1SDATA3

H3

AO1SDATA2

H2

AO1SDATA1

H1

AO1SDATA0

J4

AO1LRCK

J3

AO1BCK

J2

AO1MCLK

J1

AO2SDATA0

K1

AO2LRCK

K2

AO2BCK

K3

AO2MCLK

K4

ASPDIF

L3

ASPDIF2

L4

VOB0

L2

VOB1

L1

VOB2

M4

VOB3

M3

VOB4

M2

VOB5

M1

VOB6

N4

VOB7

N3

VOG0

N2

VOG1

N1

VOG2

P4

VOG3

P3

VOG4

P2

VOG5

P1

VOG6

T1

VOG7

T2

VOR0

T3

VOR1

T4

VOR2

U1

VOR3

U2

VOR4

U3

VOR5

U4

VOR6

V1

VOR7

V2

VOPCLK

V3

VOHSYNC

V4

VOVSYNC

W1

VODE

W2

JTRST#

W3

JTDI

W4

JTMS

Y1

JTCK

Y2

JRTCK

Y3

JTDO

Y4

GND

L14

GND

L15

GND

L16

GND

L17

GND

L18

GND

M14

GND

M15

GND

M16

GND

M17

GND

M18

GND

N14

GND

N15

GND

N16

GND

N17

GND

N18

GND

P11

GND

P12

GND

P13

GND

P14

GND

P15

GND

P16

GND

P17

GND

P18

GND

R11

GND

R12

GND

R13

GND

R14

GND

R15

GND

R16

GND

R17

GND

R18

PARB#

D27

PARE#

D28

PACE#

E25

PACLE

E26

PAALE

E27

PAWE#

E28

ELREQ

F25

ECLK

F26

ECNTL0

F27

ECNTL1

F28

EDATA0

G25

EDATA1

G26

EDATA2

G27

EDATA3

G28

EDATA4

H25

EDATA5

H26

EDATA6

H27

EDATA7

H28

ELPS

J25

ELINKON

J26

ORESET#

J27

OIRI

J28

OIRO

K25

ICS1#

K26

ICS0#

K27

IDA2

K28

IDA0

L25

IDA1

L26

IINTRQ

L27

IDMACK#

L28

IIORDY

M25

IDIOR#

M26

IDIOW#

M27

IDMARQ

M28

IDD15

N25

IDD0

N26

IDD14

N27

IDD1

N28

IDD13

P25

IDD2

P26

IDD12

P27

IDD3

P28

IDD11

T28

IDD4

T27

IDD10

T26

IDD5

T25

IDD9

U28

IDD6

U27

IDD8

U26

IDD7

U25

IRESET#

V28

DDETECT

V27

DCLK

V26

DCMD

V25

DDATA0

W28

DDATA1

W27

DDATA2

W26

DDATA3

W25

MDETECT

Y28

MCLK

Y27

MBS

Y26

MDATA0

Y25

MDATA1

AA28

MDATA2

AA27

MDATA3

AA26

STSCLK

AA25

STSDOUT

AB28

STSDIN

AB27

SPWRSEL

AB26

SDETECT

AB25

SCMDVCC

AC28

SRST

AC27

SCLK

AC26

SDATA

AC25

GND

T11

GND

T12

GND

T13

GND

T14

GND

T15

GND

T16

GND

T17

GND

T18

GND

U11

GND

U12

GND

U13

GND

U14

GND

U15

GND

U16

GND

U17

GND

U18

GND

V11

GND

V12

GND

V13

GND

V14

GND

V15

GND

V16

GND

V17

GND

V18

DV

RE

F

2

AE8

DV

RE

F

0

AE9

DV

RE

F

1

AE2

0

DV

RE

F

3

AE2

1

RDQ

32

AA1

RDQ

33

AA2

RDQ

34

AA3

RDQ

35

AB1

RDQ

36

AB2

RDQ

37

AB3

RDQ

38

AC

1

RDQ

39

AC

2

RDQ

S

4

AC

3

RDQ

M

4

AD

1

RDQ

M

5

AD

2

RDQ

S

5

AD

3

RDQ

40

AE1

RDQ

41

AE2

RDQ

42

AE3

RDQ

43

AF

1

RDQ

44

AF

2

RDQ

45

AF

3

RDQ

46

AG

1

RDQ

47

AG

2

RCLK

0

AH

1

RCLK

0

#

AH

2

RDQ

0

AH

3

RDQ

1

AG

3

RDQ

2

AH

4

RDQ

3

AG

4

RDQ

4

AF

4

RDQ

5

AH

5

RDQ

6

AG

5

RDQ

7

AF

5

RDQ

S

0

AH

6

RDQ

M

0

AG

6

RDQ

M

1

AF

6

RDQ

S

1

AH

7

RDQ

8

AG

7

RDQ

9

AF

7

RDQ

10

AH

8

RDQ

11

AG

8

RDQ

12

AF

8

RDQ

13

AH

9

RDQ

14

AG

9

RDQ

15

AF

9

RW

E

#

AH

1

0

R

C

AS#

AG

1

0

R

R

AS#

AF

1

0

RCS

#

AH

1

1

R

BA0

AG

1

1

R

BA1

AF

1

1

RA

10

AH

1

2

RA

0

AG

1

2

RA

1

AF

1

2

RA

2

AH

1

3

RA

3

AG

1

3

RA

4

AF

1

3

RA

5

AH

1

4

RA

6

AG

1

4

RA

7

AF

1

4

RA

8

AH

1

5

RA

9

AG

1

5

RA

11

AF

1

5

RA

12

AH

1

6

RA

13

AG

1

6

RCK

E

AF

1

6

RDQ

16

AH

1

7

RDQ

17

AG

1

7

RDQ

18

AF

1

7

RDQ

19

AH

1

8

RDQ

20

AG

1

8

RDQ

21

AF

1

8

RDQ

22

AH

1

9

RDQ

23

AG

1

9

RDQ

S

2

AF

1

9

RDQ

M

2

AH

2

0

RDQ

M

3

AG

2

0

RDQ

S

3

AF

2

0

RDQ

24

AH

2

1

RDQ

25

AG

2

1

RDQ

26

AF

2

1

RDQ

27

AH

2

2

RDQ

28

AG

2

2

RDQ

29

AF

2

2

RDQ

30

AH

2

3

RDQ

31

AG

2

3

RCLK

1

AF

2

3

RCLK

1

#

AH

2

4

RDQ

48

AG

2

4

RDQ

49

AF

2

4

RDQ

50

AH

2

5

RDQ

51

AG

2

5

RDQ

52

AF

2

5

RDQ

53

AH

2

6

RDQ

54

AG

2

6

RDQ

55

AH

2

7

RDQ

S

6

AH

2

8

RDQ

M

6

AG

2

8

RDQ

M

7

AG

2

7

RDQ

S

7

AF

2

8

RDQ

56

AF

2

7

RDQ

57

AF

2

6

RDQ

58

AE2

8

RDQ

59

AE2

7

RDQ

60

AE2

6

RDQ

61

AD

2

8

RDQ

62

AD

2

7

RDQ

63

AD

2

6

RV

DD

AA4

RV

DD

AB4

RV

DD

AC

4

RV

DD

AD

4

RV

DD

AE4

RV

DD

AE5

RV

DD

AE6

RV

DD

AE7

RV

DD

AE1

0

RV

DD

AE1

1

RV

DD

AE1

2

RV

DD

AE1

3

RV

DD

AE1

6

RV

DD

AE1

7

RV

DD

AE1

8

RV

DD

AE1

9

RV

DD

AE2

2

RV

DD

AE2

3

RV

DD

AE2

4

RV

DD

AE2

5

RV

DD

AD

2

5

AT

P1

D2

AVD

D

_

APL

L

0

C2

AVD

D

_

APL

L

1

B1

AVD

D

_

VPL

L

A1

A

V

DD_DM

P

LL0

C1

A

V

DDRK

P

C3

AVD

D

YKP

B5

A

V

DDB

G

K

P

B6

DA

CV

RE

F

B7

DV

DDK

P

C6

OX

TA

L

O

A2

OX

TA

L

I

B2

NC

A5

NC

D6

A

V

DD_DM

P

LL1

D3

AT

P2

D1

C

APVG

N

D

E5

+

CE22

47uF/16v

C10UF16V/D5H11

TP4

VCXO1

TP/SMD/D1.0

TP3

IOG_Y4

TP/SMD/D1.0

R35

4.7K

R0603/SMD

LED1

LED DIP2.54

LED/DIP/P2.54

C116

0.1uF

C0603/SMD

TP1

IOR_Y6

TP/SMD/D1.0

C117

0.1uF

C0603/SMD

30/129

Summary of Contents for LCT3285TAJ

Page 1: ......

Page 5: ... 3 129 ...

Page 6: ... 0 12 0 12 0 0 1 3 124 1 3 5 3 6 27 8 6 27 1 7 12 60 26 9 1 7 12 2 1 7 12 3 1 4 2 4 129 ...

Page 7: ...12 6 6 7 1 3 0 1 3 1 3 7 3 4 4 5 129 ...

Page 40: ...38 129 ...

Page 41: ...39 129 ...

Page 42: ...40 129 ...

Page 43: ...41 129 ...

Page 44: ...42 129 ...

Page 45: ...43 129 ...

Page 46: ...44 129 ...

Page 47: ...45 129 ...

Page 48: ...46 129 ...

Page 49: ...47 129 ...

Page 50: ...48 129 ...

Page 51: ...49 129 ...

Page 52: ...50 129 ...

Page 53: ...51 129 ...

Page 54: ...52 129 ...

Page 55: ...53 129 ...

Page 56: ...54 129 ...

Page 57: ...55 129 ...

Page 58: ...56 129 ...

Page 59: ...57 129 ...

Page 60: ...58 129 ...

Page 61: ...59 129 ...

Page 62: ...60 129 ...

Page 63: ...61 129 ...

Page 64: ...62 129 ...

Page 72: ...70 129 ...

Page 73: ...71 129 ...

Page 74: ...72 129 ...

Page 75: ...73 129 ...

Page 76: ...74 129 ...

Page 77: ...75 129 ...

Page 106: ...Figure 9 2 Packing method 104 129 ...

Page 108: ...11 MECHANICAL CHARACTERISTICS 奇美電子股份有限公司 CHI MEI 106 129 ...

Page 109: ...奇美電子股份有限公司 CHI MEI 107 129 ...

Page 110: ...108 129 ...

Page 120: ...118 129 ...

Page 121: ...119 129 ...

Page 122: ...120 129 ...

Page 128: ...3 Cables Standard for Upgrade Board 126 129 ...

Page 129: ...127 129 ...

Page 130: ...128 129 ...

Page 131: ...129 129 ...