A

B

C

D

E

F

G

H

A

B

C

D

E

F

G

H

2

1

3

4

5

6

7

8

2

1

3

4

5

6

7

8

D16

C16

D15

A16

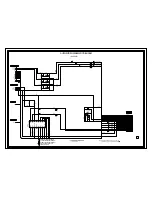

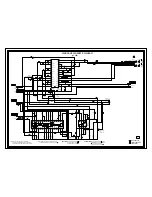

IC801

TC90288XBG

SCALER IC

C15

D18

A19

B19

C19

D19

A20

B20

C20

D20

B21

C22

C21

D21

D22

A21

E19

A17

B17

C17

B15

B16

A11

A10

C11

E12

D12

C10

D11

D10

E10

A8

A9

B9

B10

A12

A14

B12

B14

A18

B18

C18

D17

E17

A15

H25

J23

AC24

G4

F3

Y5

H1

J2

J24

G22

IC801

TC90288XBG

SCALER IC

E7

E11

E16

E20

G5

L5

L22

T5

T22

Y22

AB20

E9

E18

J5

J22

V5

V22

AB18

A1

A2

A13

A25

A26

B1

B2

B13

B25

B26

C3

C13

C24

D4

D13

D23

E6

E5

E13

E14

E22

E21

M11

L11

L12

L13

L14

L15

L16

F5

F22

M12

M13

M14

M15

M16

N11

N12

N13

N14

N15

N16

N5

N22

P1

P2

P4

P5

P11

P12

P13

P14

P15

P16

T11

T12

T13

T14

T15

T16

W1

W2

P22

P23

P24

P25

P26

R11

R12

R13

R14

R15

R16

P3

AA22

AA5

AD24

AD17

AE17

AE25

AE26

AF25

AF26

AF17

AB17

AB21

AB22

AC17

AC23

W4

W5

W3

AC21

C14

D14

N24

N23

G24

G25

H23

H24

K24

L23

G2

E4

D3

G23

F26

B11

C12

E3

F4

H3

IC807

PST3229NR

RESET IC

1

2

3

4

5

D801

MCL4148

W810

W811

C893

47

4V

V-S

C892

47

4V

V-S

C843

0.1

B

C891

0.01

B

C898 0.01 B

C899 0.01 B

C807 0.01 B

C811 0.01 B

C812 0.01 B

C813 0.01 B

C814 0.01 B

C815 0.01 B

C816 0.01 B

C824 0.01 B

C825 0.01 B

C826 0.01 B

C827 0.01 B

C828 0.01 B

C829 0.01 B

C830 0.01 B

C818 0.01 B

C819 0.01 B

C897 0.01 B

C822 0.1 B

C895

0.01

B

C806

0.01

B

C896 0.1 B

C880

0.1

B

C881

0.01

B

C886

0.01

B

C890

0.01

B

C889

0.01

B

C888

0.01

B

C887

0.01

B

C885

0.01

B

C884

0.01

B

C882

0.01

B

C883

0.01

B

C894

0.01

B

C831

0.01

B

C856

0.1

B

C820

47

4V

V-S

C821

47

4V

V-S

C879

47

4V

V-S

C871

1

50V

V-S

R831

100

R859

10K

R858

1K

R802

2.7K

R830

10K

R832

100

OF PRINTING AND SUBJECT TO CHANGE WITHOUT NOTICE

NOTE:THIS SCHEMATIC DIAGRAM IS THE LATEST AT THE TIME

DURING PLAYBACK.

MEASURED WITH THE DIGITAL TESTER

NOTE:THE DC VOLTAGE EACH PART WAS

L819

22uH

NLCV32

L817

22uH

NLCV32

L821

22uH

NLCV32

P.CON+3.3V

D_1.5V

GND

D_3.3V

GND

SCALER_V_OUT

D_1.5V

P.CON+1.5V

P.CON+3.3V

P.CON+3.3V

P.CON+2.5V

GND

P.CON+1.5V

D_3.3V

GND

P.CON+2.5V

SCALER_V_OUT

SDA

SCL

GND

G-32

G-31

(4/5 DRAM VDD)

(5/5 SCALER VDD)

(LCD PCB)

SCALER2 SCHEMATIC DIAGRAM

PCB340

TEDB66

TST2_IN[0]

TST2_IN[1]

TST2_IN[3]

TST2_IN[2]

TST2_IN[4]

TSTD_IN[0]

TSTD_IN[1]

TSTD_IN[2]

TSTD_IN[3]

TSTD_IN[4]

TSTD_IN[6]

TSTD_IN[7]

TSTD_IN[8]

TSTD_IN[9]

TSTD_IN[11]

TSTD_IN[14]

TSTD_IN[12]

TSTD_IN[13]

TSTD_IN[15]

TSTD_IN[10]

TSTD_IN[5]

TSTOE_IN

TST_HD_IN

TST_VD_IN

TSTCKDSP

TSTCK108

TRST

DIG_HD_OUT

DIG_CLK_OUT

DIG_VD_OUT

DIG_FIELD_OUT

DIG_OUT[4]

DIG_OUT[7]

DIG_OUT[5]

DIG_OUT[6]

DIG_OUT[0]

DIG_OUT[1]

DIG_OUT[2]

DIG_OUT[3]

TDI

TMS

TDO

TCK

TSTMODE[2]

TSTMODE[1]

TSTMODE[0]

TSTMODE[4]

TSTMODE[3]

MBIST

BUSSEL

RESET

SDA

CSYNC_IN

SYNC_OUT

VBIREADY

DTCLK

DTMB

SCL

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDS

VDDS

VDDS

VDDS

VDDS

VDDS

VDDS

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

VSS12

SMODE

TMODE

MONITOR

DRAM2GND1

DRAM21VDD3

DRAM2GND3

DRAM21VDD1

DRAM2GND6

DRAM21VDD2

DRAM2GND2

DRAM21VDD5

DRAM11VDD2

DRAM1GND2

DRAM12VDD1

DRAM1GND3

DRAM22VDD1

DRAM2GND5

DRAM21VDD4

DRAM2GND4

DRAM11VDD1

DRAM1GND1

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

OUT

NC

IN

NC

GND

NC

NC

0.2

0.3

3.3

3.3

0

FROM/TO DECODER

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

NC

3.3

0

3.3

3.3

0

0

0

0

0

2.3

1.5

0

1.5

0

1.5

0

1.5

0

1.5

0

1.5

0

1.5

0

1.5

0

1.5

0

1.5

1.5

1.5

1.5

1.5

1.5

1.5

1.5

1.5

1.5

1.5

1.5

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

3.3

3.3

3.3

3.3

3.3

3.3

3.3