MC96F6432

204

June 22, 2018 Ver. 2.9

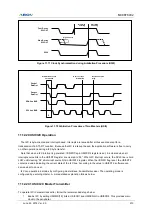

11.12.10.5 USI0 Asynchronous Data Reception

To receive asynchronous data frame, the UART includes a clock and data recovery unit. The clock recovery

logic is used for synchronizing the internally generated baud-rate clock to the incoming asynchronous serial

frame on the RXD0 pin.

The data recovery logic samples and low pass filters the incoming bits, and this removes the noise of RXD0 pin.

The next figure illustrates the sampling process of the start bit of an incoming frame. The sampling rate is 16

times of the baud-rate in normal mode and 8 times the baud-rate for double speed mode (DBLS0=1). The

horizontal arrows show the synchronization variation due to the asynchronous sampling process. Note that larger

time variation is shown when using the double speed mode.

Figure 11.61 Asynchronous Start Bit Sampling (USI0)

When the receiver is enabled (RXE0=1), the clock recovery logic tries to find a high-to-low transition on the

RXD0 line, the start bit condition. After detecting high to low transition on RXD0 line, the clock recovery logic

uses samples 8, 9 and 10 for normal mode to decide if a valid start bit is received. If more than 2 samples have

logical low level, it is considered that a valid start bit is detected and the internally generated clock is

synchronized to the incoming data frame. And the data recovery can begin. The synchronization process is

repeated for each start bit.

As described above, when the receiver clock is synchronized to the start bit, the data recovery can begin. Data

recovery process is almost similar to the clock recovery process. The data recovery logic samples 16 times for

each incoming bits for normal mode and 8 times for double speed mode, and uses sample 8, 9 and 10 to decide

data value.

If more than 2 samples have low levels, the received bit is considered to a logic

‘0’ and if more than 2

samples have high levels, the received bit is considered to a logic

‘1’. The data recovery process is then repeated

until a complete frame is received including the first stop bit. The decided bit value is stored in the receive shift

register in order. Note that the Receiver only uses the first stop bit of a frame. Internally, after receiving the first

stop bit, the Receiver is in idle state and waiting to find start bit.

Figure 11.62 Asynchronous Sampling of Data and Parity Bit (USI0)

RXD0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

1

BIT n

1

2

3

4

5

6

7

8

1

Sample

(DBLS0 = 0)

Sample

(DBLS0 = 1)

RXD0

0

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

1

2

3

IDLE

BIT0

START

0

1

2

3

4

5

6

7

8

1

2

Sample

(DBLS0 = 0)

Sample

(DBLS0 = 1)

Summary of Contents for MC96F6432 Series

Page 24: ...MC96F6432 24 June 22 2018 Ver 2 9 4 Package Diagram Figure 4 1 48 Pin LQFP 0707 Package...

Page 25: ...MC96F6432 June 22 2018 Ver 2 9 25 Figure 4 2 44 Pin MQFP Package...

Page 26: ...MC96F6432 26 June 22 2018 Ver 2 9 Figure 4 3 32 Pin LQFP Package...

Page 27: ...MC96F6432 June 22 2018 Ver 2 9 27 Figure 4 4 32 Pin SOP Package...

Page 28: ...MC96F6432 28 June 22 2018 Ver 2 9 Figure 4 5 28 Pin SOP Package...