AXI Bridge for PCI Express v2.4

106

PG055 June 4, 2014

Appendix C:

Additional Resources and Legal Notices

Revision History

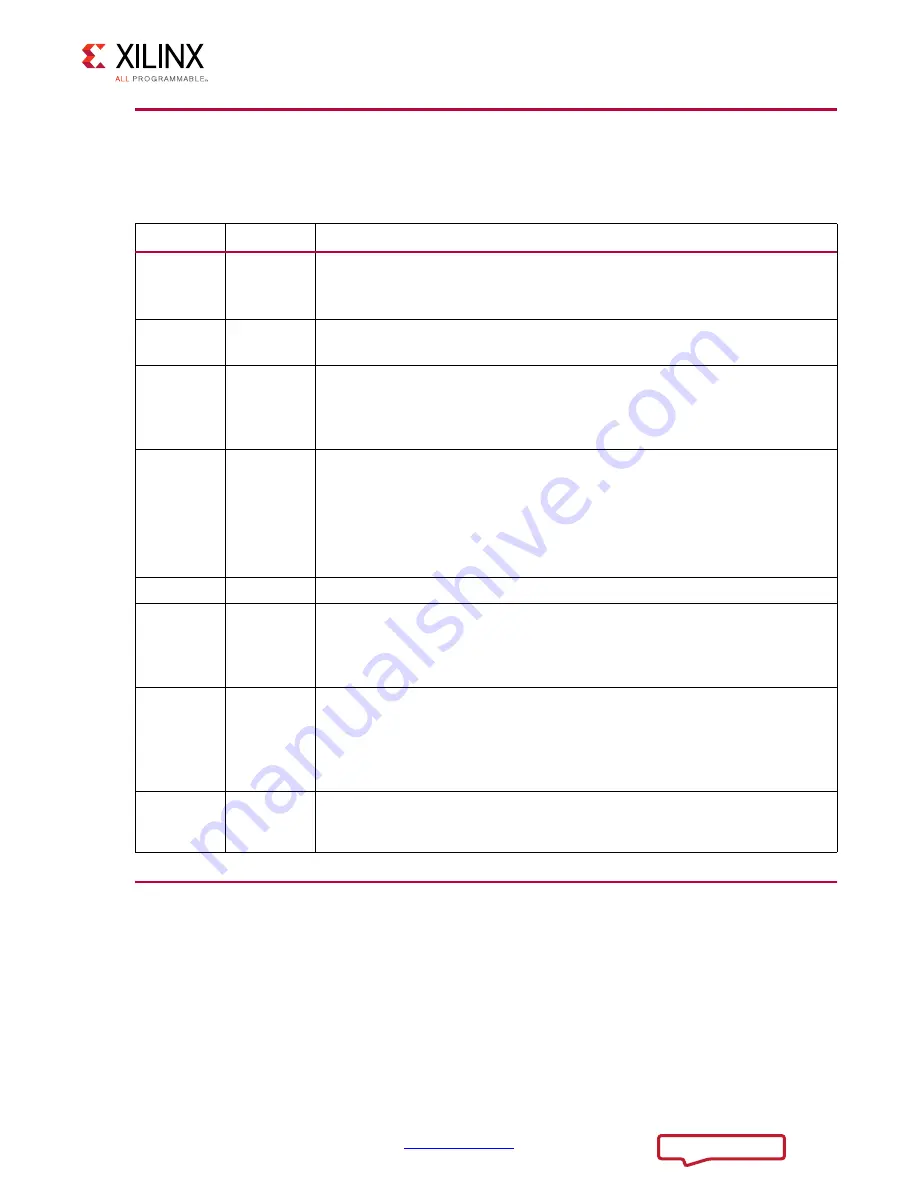

The following table shows the revision history for this document.

Please Read: Important Legal Notices

The information disclosed to you hereunder (the "Materials") is provided solely for the selection and use of Xilinx products. To the

maximum extent permitted by applicable law: (1) Materials are made available "AS IS" and with all faults, Xilinx hereby DISCLAIMS

ALL WARRANTIES AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING BUT NOT LIMITED TO WARRANTIES OF

MERCHANTABILITY, NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and (2) Xilinx shall not be liable (whether

in contract or tort, including negligence, or under any other theory of liability) for any loss or damage of any kind or nature related

to, arising under, or in connection with, the Materials (including your use of the Materials), including for any direct, indirect, special,

incidental, or consequential loss or damage (including loss of data, profits, goodwill, or any type of loss or damage suffered as a

result of any action brought by a third party) even if such damage or loss was reasonably foreseeable or Xilinx had been advised

of the possibility of the same. Xilinx assumes no obligation to correct any errors contained in the Materials or to notify you of

Date

Version

Revision

06/02/2014

2.4

• Updated for core v2.4.

• Added new device support.

• Removed the

axi_aclk

and

axi_ctl_aclk

input ports.

04/02/2014

2.3

• Updated simulation information.

• Minor changes and updates.

12/18/2013

2.3

• Updated for core v2.3.

• Updated Example Design chapter.

• Updated parameter changes and port changes in Migrating and Updating

chapter.

10/02/2013

2.2

• Updated for core v2.2.

• Updated resource utilization numbers.

• Added information about the Shared Logic feature.

• Added example design information.

• Added port and parameter upgrade information.

• Added transceiver debug information.

03/20/2013

2.0

Updated for core v2.0, and for Vivado Design Suite-only support.

12/18/2012

1.2

• Updated core v1.06a, ISE Design Suite 14.4, and Vivado Design Suite

2012.4.

• Updated

Chapter 4, Customizing and Generating the Core

• Added

10/16/2012

1.1

• Updated core v1.05a, ISE Design Suite 14.3, and Vivado Design Suite

2012.3.

• Added

,

Customizing and Generating the Core

.

• Major updates to PCIe Clock Integration.

• Added Unsupported Request to Upstream Traffic and Clock Frequencies.

07/25/2012

1.0

Initial Xilinx release. This release is for core version 1.04.a with ISE Design

Suite 14.2 and Vivado Design Suite 2012.2. This document replaces DS820,

LogiCORE IP AXI Bridge for PCI Express Data Sheet

.