FOR MOBILE APPLICATIONS

W25Q256FV

- 77 -

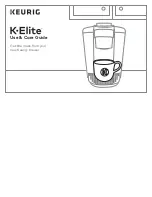

8.2.39

Read JEDEC ID (9Fh)

For compatibility reasons, the W25Q256FV provides several instructions to electronically determine the

identity of the device. The Read JEDEC ID instruction is compatible with the JEDEC standard for SPI

compatible serial memories that was adopted in 2003. The instruction is initiated by driving the /CS pin low

and shifting the instruction code “9Fh”. The JEDEC assigned Manufacturer ID byte for Winbond (EFh) and

two Device ID bytes, Memory Type (ID15-ID8) and Capacity (ID7-ID0) are then shifted out on the falling

edge of CLK with most significant bit (MSB) first as shown in Figure 43a & 43b. For memory type and

capacity values refer to Manufacturer and Device Identification table.

/CS

CLK

DI

(IO

0

)

DO

(IO

1

)

Mode 0

Mode 3

0

1

2

3

4

5

6

7

Instruction (9Fh)

High Impedance

8

9

10

12

13

14

15

Capacity ID7-0

/CS

CLK

DI

(IO

0

)

DO

16

(IO

1

)

17

18

19

20

21

22

23

Manufacturer ID (EFh)

24

25

26

28

29

30

7

6

5

4

3

2

1

0

*

27

15

Mode 0

Mode 3

11

7

6

5

4

3

2

1

0

*

Memory Type ID15-8

= MSB

*

Figure 43a. Read JEDEC ID Instruction (SPI Mode)

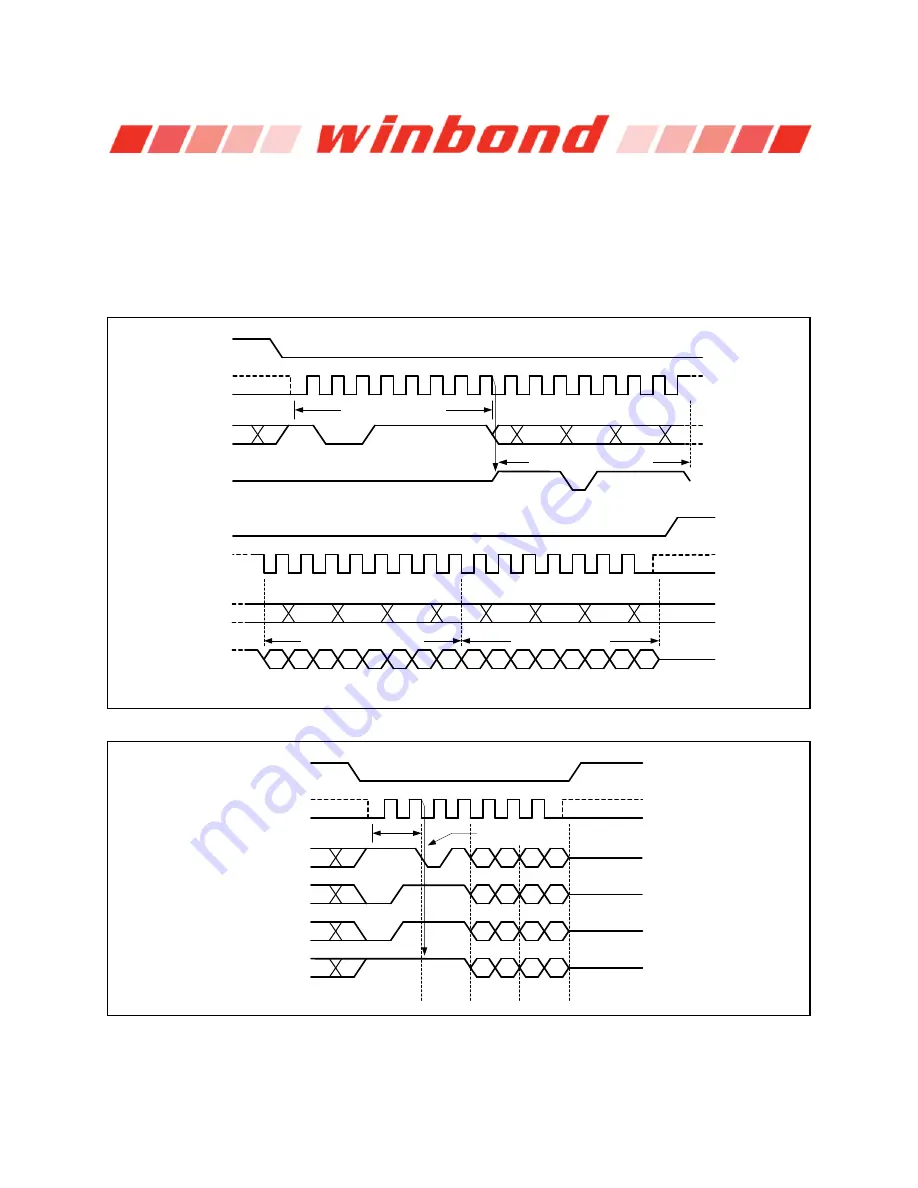

/CS

CLK

Mode 0

Mode 3

0

1

IO

0

IO

1

IO

2

IO

3

9Fh

2

3

4

5

12

8

13

9

14

10

15

11

EFh

6

4

0

5

1

6

2

7

3

ID15-8

ID7-0

IOs switch from

Input to Output

Instruction

Mode 0

Mode 3

Figure 43b. Read JEDEC ID Instruction (QPI Mode)