EVK-IRIS-W10 - User guide

UBX-23007837 - R03

Hardware description

Page 22 of 43

C1-Public

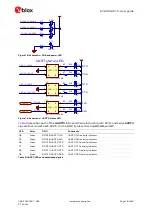

IRIS-W10 pin name

IRIS-W10 function

Resistor/Jumper enable

Interface IC function

B14

GPIO6/JTAG-TCK

R1/J15

FTDI-JTAG-TCK, Pin 16,

U108

B12

GPIO8/JTAG-TDI

R3/J36

FTDI-

JTAG-TDI, Pin 17, U108

A12

GPIO9/JTAG-TDO

R4/J34

FTDI-

JTAG-TDO, Pin 18, U108

A14

GPIO7/JTAG-TMS

R5/J35

FTDI-

JTAG-TMS Pin 19, U108

B11

GPIO10/JTAG-RESETn

R6/J37

FTDI-

JTAG-RESETn, Pin 22, U108

-

JTAG-Bootn

R7

FTDI-

Pin 23

,

U108

M9

GPIO 4/SPI-CLK

R8

FTDI-SPI-CLK,

Pin 26, U108

M10

GPIO 2/SPI-MOSI

R9

FTDI-SPI-MOSI,

Pin 27, U108

N10

GPIO 3/SPI-MISO

R37

FTDI-SPI-MISO,

Pin 28, U108

M11

GPIO 0/SPI-CS

R38

FTDI-SPI-CS,

Pin 29, U108

N11

GPIO 1/SPI-WP

R41

FTDI-SPI-WP,

Pin 30, U108

M2

GPIO 21/SPI-HD

R42

FTDI-SPI-HD,

Pin 32, U108

A10

GPIO 26/UART-TXD

R52

FTDI-UART-RXD, Pin 39, U108, Pin 17, U109

B9

GPIO 24/UART-RXD

R53

FTDI-UART-TXD, Pin 38, U108, Pin 1, U109

B8

GPIO 19/UART-RTS

R54

FTDI-UART-RTS, Pin 40, U108, Pin 19, U109

A9

GPIO 20/UART-CTS

R55

FTDI-UART-CTS, Pin41, U108, Pin 6, U109

A11

GPIO 11/UART-DTR

R56

FTDI-UART-DTR, Pin 43, U108, Pin 18, U109

B10

GPIO 12/UART-DSR

R57

FTDI-UART-DSR, Pin 44, U108, Pin 4, U109

-

-

R58

Pin 48, U108

-

-

R59

Pin 52, U108

-

-

R60

Pin 53, U108

-

-

R61

Pin 54, U108

-

-

R63

Pin 55, U108

-

-

R64

Pin 57, U108

-

-

R65

Pin 58, U108

-

-

R66

Pin 59, U108

Table 8: Main COM port connections

UART3 clock signal from IRIS-W10 pin

F3,

GPIO 25

is multiplexed by RMII clock signal.

R282/R279

are

intended to

demultiplex the two signals

R279

is populated by default and

connects to

RMII clock, by disconnecting

R279

and populating

R282

with

0R, GPIO25

will be

connected to pin

8

on header

J48.

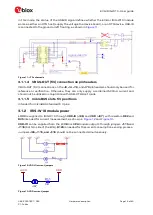

3.6

JTAG/SWD debug interfaces

There are two interfaces for debugging IRIS-W10 either

JTAG

or

SWD

. When powering up or

resetting the EVK-IRIS-W10, the status of the

RF-Control

strapping pins defines the active

RF-CNTRL

SWD

JTAG

GPIOs

RF-CNTL0

F

F

F

RF-CNTL1

F

F

F

RF-CNTL2

0

F

F

RF-CNTL3

F

F

0

Table 9: RF-CTRL strap-in (F=Float)

SW8

is used to set the RF-CNTL signals to the desired status as shown in

. An

external target hardware can be attached to the

J20

header connector for firmware

programming and debug.

J20

is implemented with a 2x5 header with 1.27 mm pitch.