EVA-8M and EVA-M8 series - Hardware Integration Manual

UBX-16010593 - R06

Design-in

Page 10 of 47

Early Production Information

2.2.2

Display Data Channel (DDC) Interface

An I

2

C compatible Display Data Channel (DDC) interface is available for serial communication with a

host CPU.

☞

The SCL and SDA pins have internal pull-up resistors sufficient for most applications. However,

depending on the speed of the host and the load on the DDC lines additional external pull-up

resistors might be necessary. For speed and clock frequency see the

EVA-M8 Data Sheet [1] and

the

EVA-8M Data Sheet [2].

☞

To make use of DDC interface the

D_SEL

pin has to be left open.

☞

The EVA-8M / EVA-M8 series GNSS modules DDC interface provides serial communication with

u-blox cellular modules. See the specification of the applicable cellular module to confirm

compatibility.

2.2.3

SPI Interface

The SPI interface can be used to provide a serial communication with a host CPU. If the SPI interface

is used, UART and DDC are deactivated, because they share the same pins.

☞

To make use of the SPI interface, the

D_SEL

pin has to be connected to GND.

2.2.4

USB interface

The USB interface of the EVA-8M / EVA-M8 series GNSS modules support the full-speed data rate of

12

Mbit/s. It is compatible to the USB 2.0 FS standard. The interface requires some external

components in order to implement the physical characteristics required by the USB 2.0 specification.

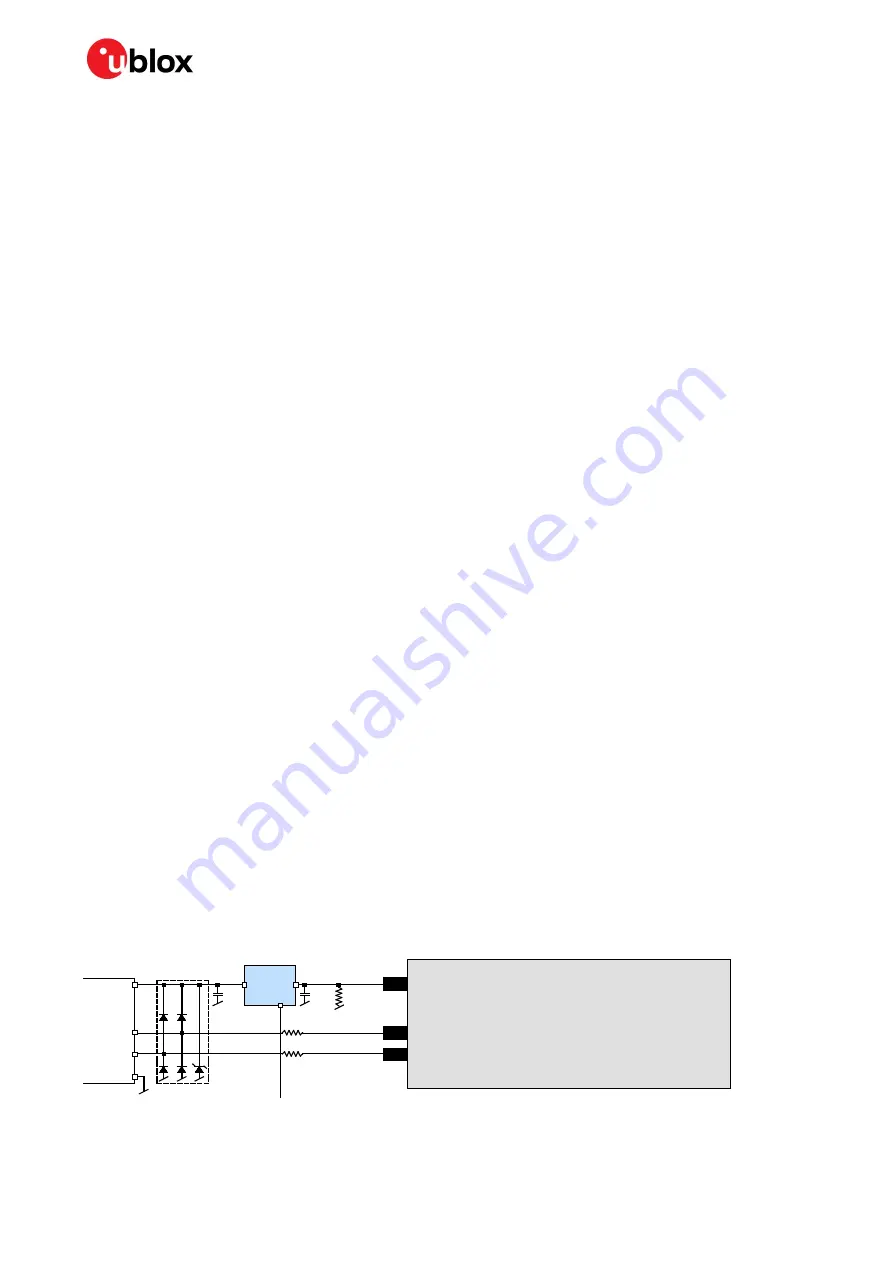

Figure 2 shows the interface pins and additional external components. In order to comply with USB

specifications, VBUS must be connected through a LDO (U1) to pin

VDD_USB

of the module. This

ensures that the internal 1.5

k

Ω

pull-up resistor on

USB_DP

gets disconnected when the USB host

shuts down VBUS.

Depending on the characteristics of the LDO (U1), for a self-powered design it is recommended to add

a pull-down resistor (R8) at its output to ensure

VDD_USB

does not float if a USB cable is not

connected, i.e. when VBUS is not present. In USB

self-powered

mode, the power supply (

VCC

) can be

turned off and the digital block is not powered. In this case, since VBUS is still available, the USB host

would still receive the signal indicating that the device is present and ready to communicate. This

should be avoided by disabling the LDO (U1) using the enable signal (EN) of the VCC-LDO or the output

of a voltage supervisor.

The interface can be used either in “self-powered” or “bus-powered” mode. The required mode can be

configured using the UBX-CFG-USB message. Also, the vendor ID, vendor string, product ID and

product string can be changed.

In order to get the 90

Ω

differential impedance in between the

USB_DM

and

USB_DP

data line, a 27

Ω

series resistor (R4, R5) must be placed into each data line (

USB_DM

and

USB_DP

).

Module

VDD_USB

LDO

VDD_USB

R4

USB_DP

USB_DM

R5

C24

C23

D2

VBUS

DP

DM

GND

US

B D

evi

ce Co

nn

ec

to

r

U1

EN

R11

EN

Figure 2: USB interface