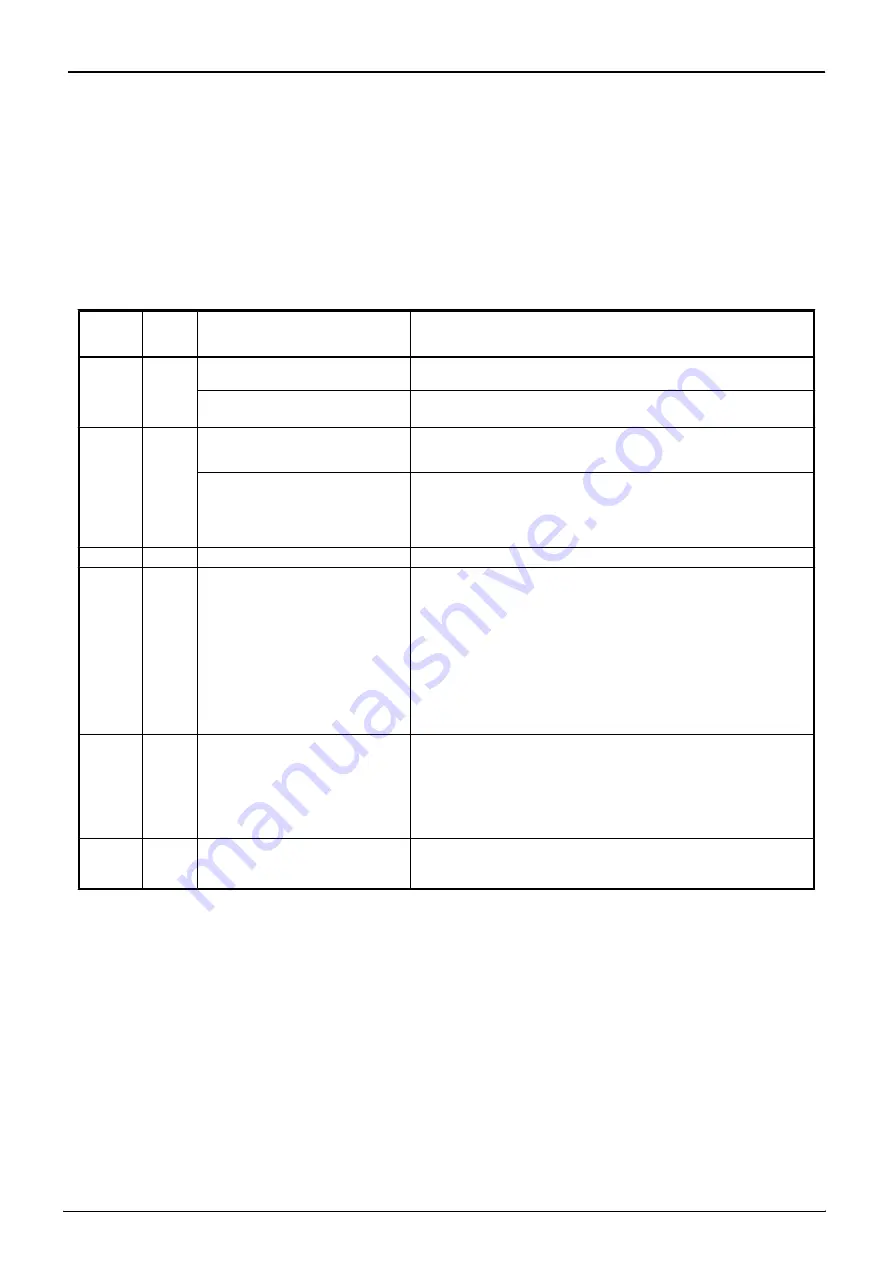

22.3.7 Transfer Format of Flash memory Chip Erase and Protect Bit Erase

This section shows a transfer format of Flash memory chip erase and protect bit erase commands. Transfer

directions in the table are indicated as follows:

Transfer direction (C→T): Controller to

TMPM3V6/M3V4

Transfer direction (C←T):

TMPM3V6/M3V4

to Controller

Number of

transfer

bytes

Transfer

direction

Transfer data

Description

1

C→T

Serial operation mode and baud rate set-

ting

Sends data to determine the serial operation mode. For detail of mode determina-

tion, refer to"22.3.5.1 Serial Operation Mode Determination".

[UART mode]

0x86

Sends 0x86. If UART mode is determined, checks if baud rate setting can be

done. If not, operation stops communications.

2

C←T

ACK response to serial operation mode

The 2nd byte of transmit data is a ACK response data to the 1st byte that corre-

sponds to the serial operation setting mode data. If the setting is possible, sets SIO/

UART. A receive enable timing is set before transmit buffer is written to the data.

[UART mode]

Normal state: 0x86

If the setting is determined to be possible, sends 0x86. If not, the operation aborts

without sending back any response.

When the controller finished to send the 1st byte of data, requires a time-out time

(5 seconds). If data (0x86) is not normally received within a time-out time, communi-

cation is not possible.

3

C→T

Operation command data (0x40)

Sends Flash memory chip erase and protect bit erase command data (0x40).

4

C←T

ACK response to the operation command

Normal state: 0x40

Abnormal state: 0xX1

Communication error: 0xX8

ACK response data to the operation command.

First, checks if 3rd byte of receive data has errors. (UART mode only) If receive er-

rors exist, sends a ACK response data 0xX8 that means abnormal communica-

tions and waits for a next operation command (3rd byte). Upper 4 bits of transmit da-

ta are undefined. (same as upper 4 bits of immediately before operation command

data.) Note that in the I/O interface, receive error check is not performed.

Then, if the 3rd byte of receive data corresponds to either operation command da-

ta in Table 22-12, receive data is echoed back. If the data does not correspond to

the command in Table 22-12, sends a ACK response data 0xX1 that means opera-

tion command errors, and waits for next operation command. (3rd byte) Upper 4

bits of transmit data are undefined. (Upper 4 bits of immediate before operation com-

mand data are used.)

5 to 16

C→T

Password data (12-byte)

0x3F81_FFF4 to 0x3F81_FFFF

If password necessity is set to "none", this data is dummy data.

If password necessity is set to "necessary", checks data in the password area. For

a method of password area data checking, refer to "22.3.5.3 Password Determina-

tion".

Compares 5th to 16th byte of receive data with 0x3F81_FFF0 to 0x3F81_FFFF of

data of Flash memory in order. If the data does not match, a password error flag

is set.

17

C→T

5th to 16th byte CHECK SUM value

Sends 5th byte to 16 byte of CHECK SUM value.

For a method of CHECK SUM calculation, refer to"22.3.5.4 CHECK SUM Calcula-

TMPM3V6/M3V4

22.

Flash Memory Operation

22.3 How to Reprogram Flash using Single Boot Mode

Page 474

2019-02-06

Содержание TMPM3V4

Страница 1: ...32 Bit RISC Microcontroller TX03 Series TMPM3V6 M3V4 ...

Страница 2: ... 2019 Toshiba Electronic Devices Storage Corporation ...

Страница 7: ...Revision History Date Revision Comment 2019 02 06 1 First Release ...

Страница 8: ......

Страница 22: ...xiv ...

Страница 52: ...TMPM3V6 M3V4 3 Processor Core 3 6 Exclusive access Page 30 2019 02 06 ...

Страница 148: ...TMPM3V6 M3V4 7 Exceptions 7 6 Exception Interrupt Related Registers Page 126 2019 02 06 ...

Страница 178: ...TMPM3V6 M3V4 9 Input Output port 9 2 Block Diagrams of Ports Page 156 2019 02 06 ...

Страница 206: ...TMPM3V6 M3V4 10 16 bit Timer Event Counters TMRB 10 7 Applications using the Capture Function Page 184 2019 02 06 ...

Страница 232: ...TMPM3V6 M3V4 11 Universal Asynchronous Receiver Transmitter Circuit UART 11 4 Operation Description Page 210 2019 02 06 ...

Страница 354: ...TMPM3V6 M3V4 14 Synchronous Serial Port SSP 14 6 Frame Format Page 332 2019 02 06 ...

Страница 419: ...TMPM3V6 M3V4 Page 397 2019 02 06 ...

Страница 420: ...TMPM3V6 M3V4 16 Analog Digital Converter ADC 16 6 Timing chart of AD conversion Page 398 2019 02 06 ...

Страница 462: ...TMPM3V6 M3V4 21 Watchdog Timer WDT 21 5 Control register Page 440 2019 02 06 ...

Страница 510: ...TMPM3V6 M3V4 22 Flash Memory Operation 22 4 Programming in the User Boot Mode Page 488 2019 02 06 ...

Страница 538: ...TMPM3V6 M3V4 25 Electrical Characteristics 25 7 Recommended Oscillation Circuit Page 516 2019 02 06 ...

Страница 541: ...26 3 TMPM3V4FWUG TMPM3V4FSUG Type LQFP64 P 1010 0 50E LPHQVLRQV TMPM3V6 M3V4 Page 519 2019 02 06 ...

Страница 544: ......