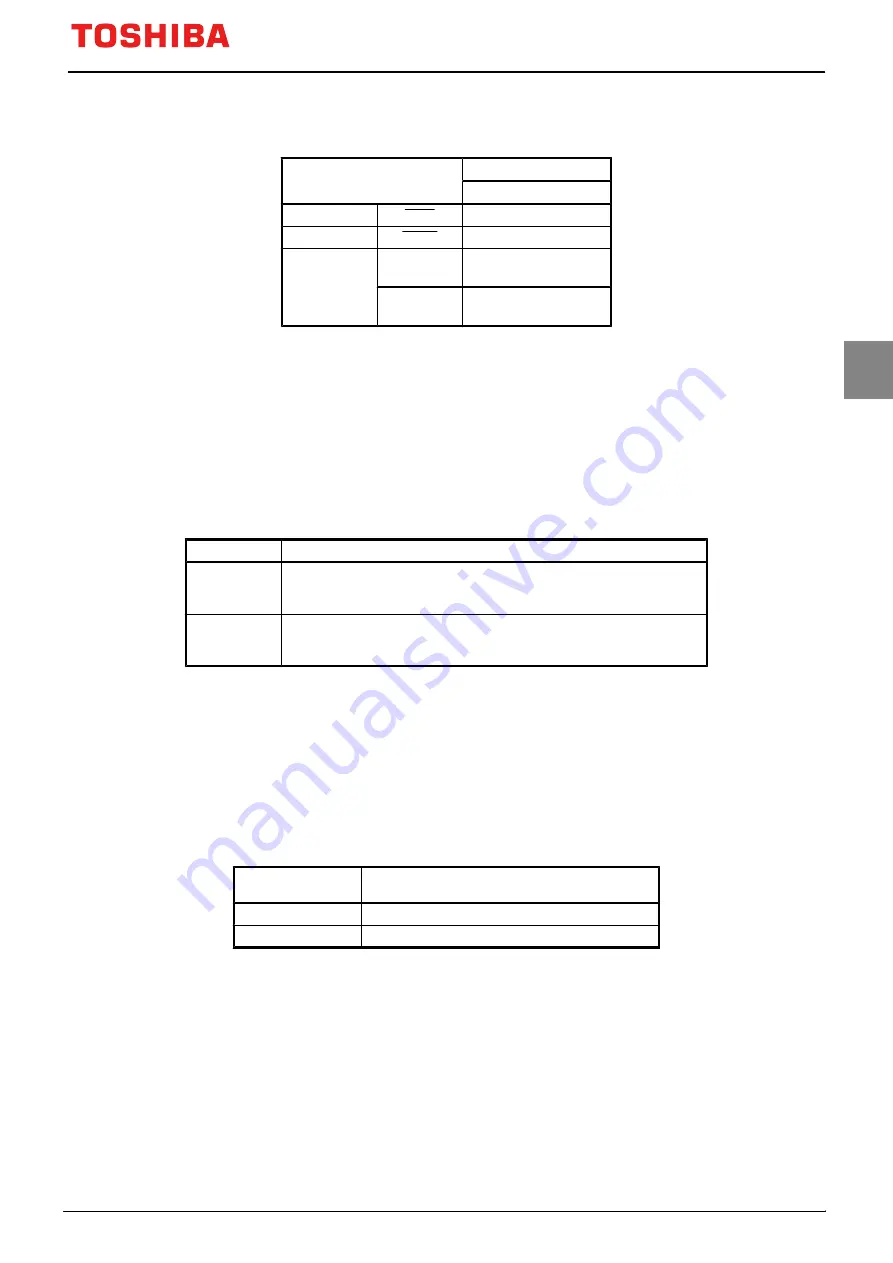

Table 22-10 Pin connection

Pin

Interface

UART

Mode setting pin

BOOT

ο

Reset pin

RESET

ο

Communication

pin

TXD0

(PE0)

ο

RXD0

(PE1)

ο

ο:used ×:unused

22.3.3 Restrictions on Internal Memories

Note that the single boot mode places restrictions on the built-in RAM and built-in flash memory as

shown in Table 22-11.

Table 22-11 Restrictions on the memories in the single boot mode

Memory

Restrictions

Internal RAM

Boot program uses the memory as a work area through 0x2000_0000 to 0x2000_03FF.

Store the program 0x2000_0400 through the end address of RAM. The start address of

the program must be even address.

Internal flash

memory

The following addresses are assigned for storing software ID information and pass-

w

o

rds. Storing program in below addresses is not recommendable.

0x3F81_FFF0 to 0x3F81_FFFF

Note:

If a password is erased data (0xFF), it is difficult to protect data secure due to an easy-to-guess pass-

word. Even if the single boot mode is not used, it is recommended to set a unique value as a password.

22.3.4 Operation Command

The boot program provides the following operation commands.

Table 22-12 Operation command data

Operation command da-

ta

Operation mode

0x10

RAM transfer

0x40

Flash memory chip erase and protect bit erase

22.3.4.1 RAM Transfer

The RAM transfer is to store data from the controller to the built-in RAM. When the transfer is com-

plete normally, a user program starts. User program can use the memory address of 0x2000_0400 or later

except 0x2000_0000 to 0x2000_03FF for the boot program. CPU will start execution from RAM store

start address. The start address must be even address.

This RAM transfer function enables user-specific on-board programming control. In order to execute

the on-board programming by a user program, use Flash memory command sequence explained in 22.2.6.

TMPM3V6/M3V4

Page 465

2019-02-06

Содержание TMPM3V4

Страница 1: ...32 Bit RISC Microcontroller TX03 Series TMPM3V6 M3V4 ...

Страница 2: ... 2019 Toshiba Electronic Devices Storage Corporation ...

Страница 7: ...Revision History Date Revision Comment 2019 02 06 1 First Release ...

Страница 8: ......

Страница 22: ...xiv ...

Страница 52: ...TMPM3V6 M3V4 3 Processor Core 3 6 Exclusive access Page 30 2019 02 06 ...

Страница 148: ...TMPM3V6 M3V4 7 Exceptions 7 6 Exception Interrupt Related Registers Page 126 2019 02 06 ...

Страница 178: ...TMPM3V6 M3V4 9 Input Output port 9 2 Block Diagrams of Ports Page 156 2019 02 06 ...

Страница 206: ...TMPM3V6 M3V4 10 16 bit Timer Event Counters TMRB 10 7 Applications using the Capture Function Page 184 2019 02 06 ...

Страница 232: ...TMPM3V6 M3V4 11 Universal Asynchronous Receiver Transmitter Circuit UART 11 4 Operation Description Page 210 2019 02 06 ...

Страница 354: ...TMPM3V6 M3V4 14 Synchronous Serial Port SSP 14 6 Frame Format Page 332 2019 02 06 ...

Страница 419: ...TMPM3V6 M3V4 Page 397 2019 02 06 ...

Страница 420: ...TMPM3V6 M3V4 16 Analog Digital Converter ADC 16 6 Timing chart of AD conversion Page 398 2019 02 06 ...

Страница 462: ...TMPM3V6 M3V4 21 Watchdog Timer WDT 21 5 Control register Page 440 2019 02 06 ...

Страница 510: ...TMPM3V6 M3V4 22 Flash Memory Operation 22 4 Programming in the User Boot Mode Page 488 2019 02 06 ...

Страница 538: ...TMPM3V6 M3V4 25 Electrical Characteristics 25 7 Recommended Oscillation Circuit Page 516 2019 02 06 ...

Страница 541: ...26 3 TMPM3V4FWUG TMPM3V4FSUG Type LQFP64 P 1010 0 50E LPHQVLRQV TMPM3V6 M3V4 Page 519 2019 02 06 ...

Страница 544: ......