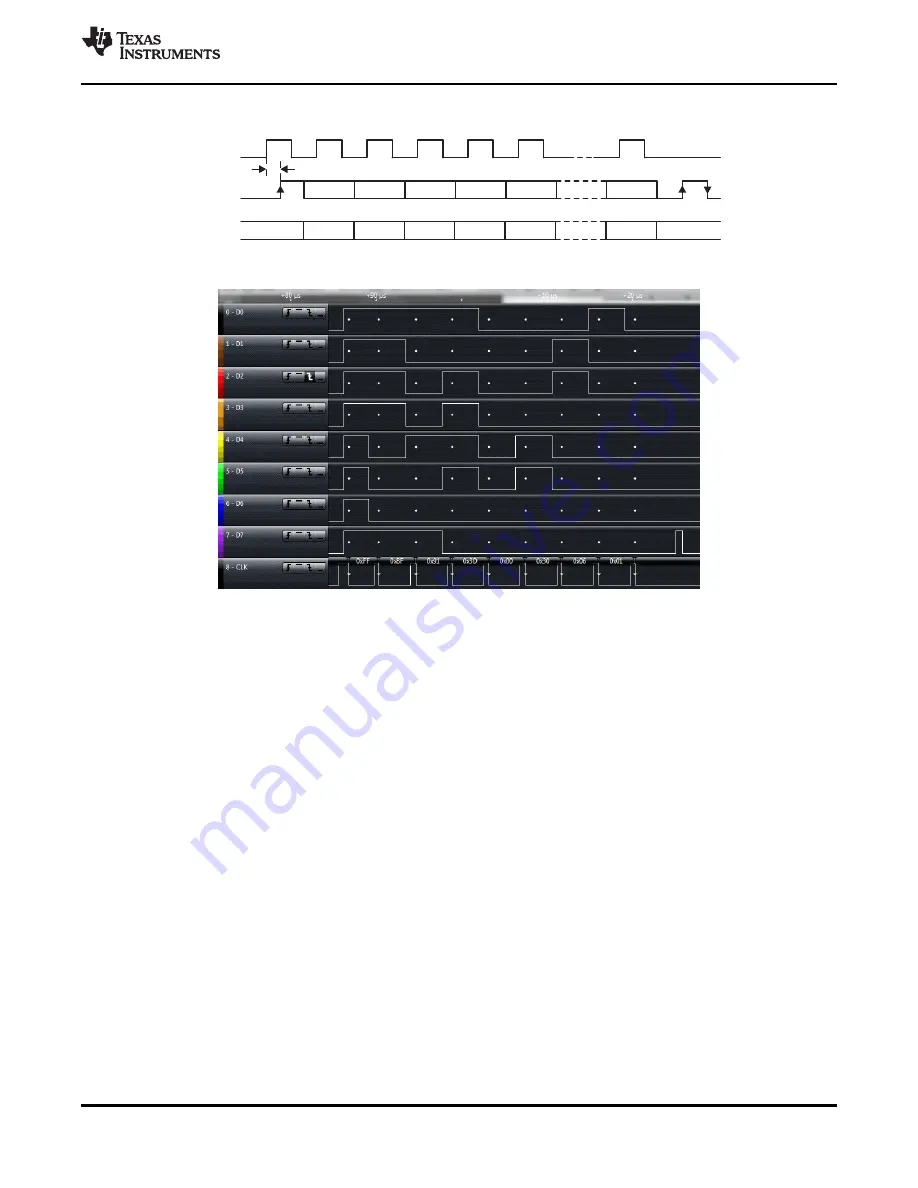

CLK

I/O_[7]

I/O_[6:0]

a0 [7]

d0 [7]

d1 [7]

d2 [7]

d3 [7]

dN [7]

a0 [6:0]

d0 [6:0]

d1 [6:0]

d2 [6:0]

d3 [6:0]

dN [6:0]

xx

xx

50 ns

Start

Condition

StopCont

Continuous Mode

37

SLOS743L – AUGUST 2011 – REVISED MARCH 2017

Product Folder Links:

Detailed Description

Copyright © 2011–2017, Texas Instruments Incorporated

Figure 6-15. Parallel Interface Communication With Continuous Stop Condition (StopCont)

Figure 6-16. Example of Parallel Interface Communication With Continuous Stop Condition

6.10.3 Reception of Air Interface Data

At the start of a receive operation (when SOF is successfully detected), B6 is set in the IRQ Status

register. An RX complete interrupt request is sent to the MCU at the end of the receive operation if the

receive data string is shorter than or equal to the number of bytes configured in the Adjustable FIFO IRQ

Levels register (0x14). An IRQ_FIFO interrupt request is sent to the MCU during the receive operation if

the data string is greater than the level set in the Adjustable FIFO IRQ Levels register (0x14). After

receiving an IRQ_FIFO or RX complete interrupt, the MCU must read the FIFO Status register (0x1C) to

determine the number of bytes to be read from the FIFO. Next, the MCU must read the data in the FIFO.

It is optional but recommended to read the FIFO Status register (0x1C) after reading FIFO data to

determine if the receive is complete. In the case of an IRQ_FIFO, the MCU should expect either another

IRQ_FIFO or RX complete interrupt. This is repeated until an RX complete interrupt is generated. The

MCU receives the interrupt request, then checks to determine the reason for the interrupt by reading the

IRQ Status register (0x0C), after which the MCU reads the data from the FIFO.

If the reader detects a receive error, the corresponding error flag is set (framing error, CRC error) in the

IRQ Status register, indicating to the MCU that reception was not completed correctly.