2 Setup

This section describes how to properly use the TPSM8286xAA0xEVM.

2.1 Setup

To operate the EVM, set jumper JP1 between ON and EN to turn on the device as shown in

Connector and Jumper Descriptions

. Connect the input supply to J1 and connect the load to J2.

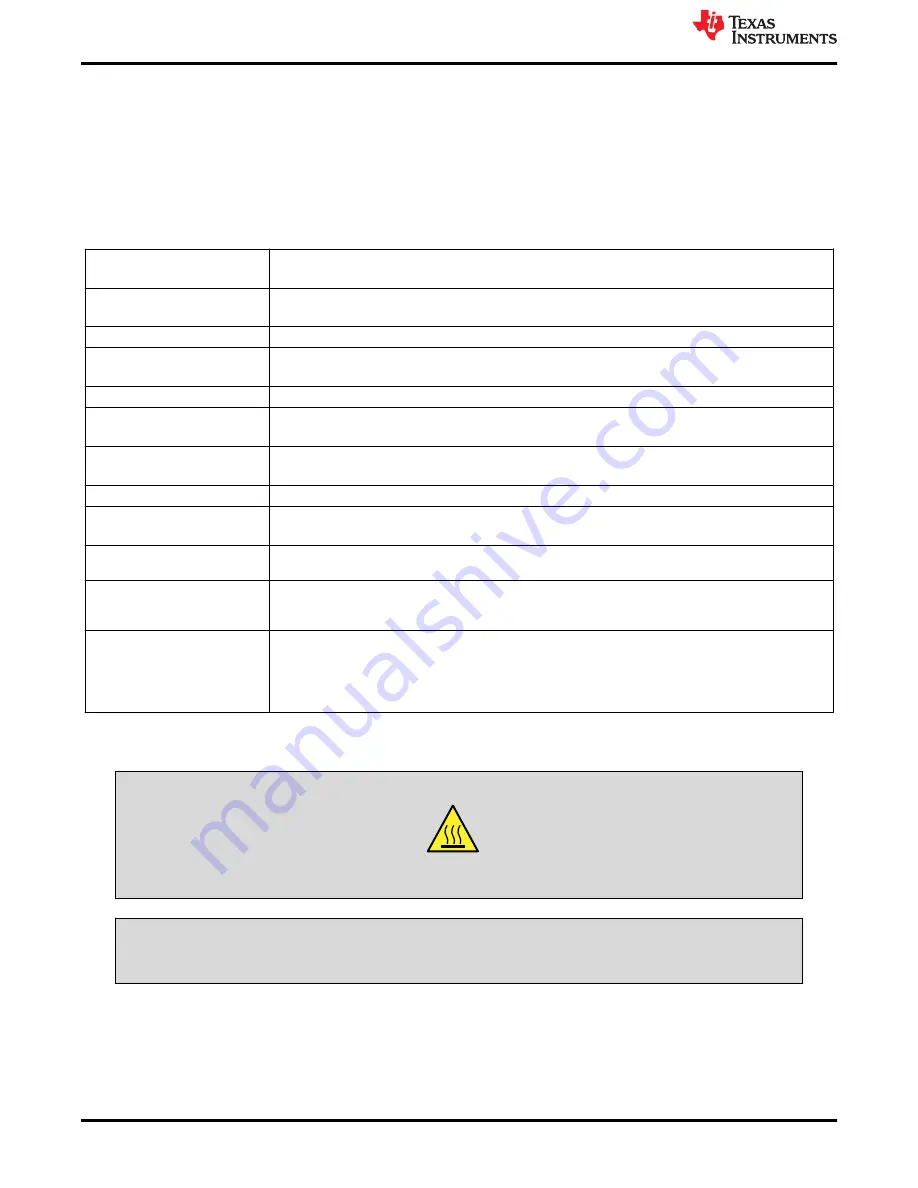

2.2 Input, Output Connector and Jumper Descriptions

J1 – VIN/GND

Input and return connections from the input supply for the EVM.

This connector supports currents over 3 A and accepts up to 16 AWG wire.

J2 – VOUT/GND

Input and return connections from the EVM to the load.

This connector supports currents over 3 A and accepts up to 16 AWG wire.

J3 – PG/GND

The PG output appears on pin 2 of this header with ground on pin 1.

J4, Pin 1 and 2 – VIN

Positive input connection from the input supply for the EVM

Do not use for currents above 3 A.

J4, Pin 3 and 4 – S+/S–

Input voltage sense connections. Measure the input voltage at this point.

J4, Pin 5 and 6 – GND

Input return connection from the input supply for the EVM.

Do not use for currents above 3 A.

J5, Pin 1 and 2 – VOUT

Output voltage connection

Do not use for currents above 3 A.

J5, Pin 3 and 4 – S+/S–

Output voltage sense connections. Measure the output voltage at this point.

J5, Pin 5 and 6 – GND

Output return connection

Do not use for currents above 3 A.

JP1 – EN

EN pin input jumper. Place the supplied jumper across ON and EN to turn on the module. Place the

jumper across OFF and EN to turn off the module.

JP2 – PG Pullup Voltage

PG pin pullup voltage jumper. Place the supplied jumper on JP2 to connect the PG pin pullup resistor to

VOUT. Alternatively, the jumper can be removed and a different voltage can be supplied on pin 1 to pull

up the PG pin to a different level. This externally applied voltage must remain below 6 V.

JP3 – VSET/MODE

VSET/MODE pin input jumper. Place the supplied jumper across PWM and VSET/MODE to operate the

IC in Forced PWM mode. Place the jumper across PFM/PWM and VSET/MODE to operate the IC in

Auto PFM/PWM mode. Remove the jumper to operate the IC with a fixed output voltage, which is set by

R4.

For the fixed output voltage configuration, R4 must be installed, R2 removed, and R1 shorted.

3 Safety Instructions

WARNING

Hot surface. Contact may cause burns. Do not touch.

WARNING

High currents may be present on the input and output. Use connectors J1 and J2 if the current exceeds 3 A.

Setup

4

TPSM8286xAA0xEVM Evaluation Module

SLVUCB0A – SEPTEMBER 2021 – REVISED NOVEMBER 2022

Copyright © 2022 Texas Instruments Incorporated