See “External Peripheral Interface (EPI)” on page 1853 for timing details for the SDRAM mode.

11.4.2.1

External Signal Connections

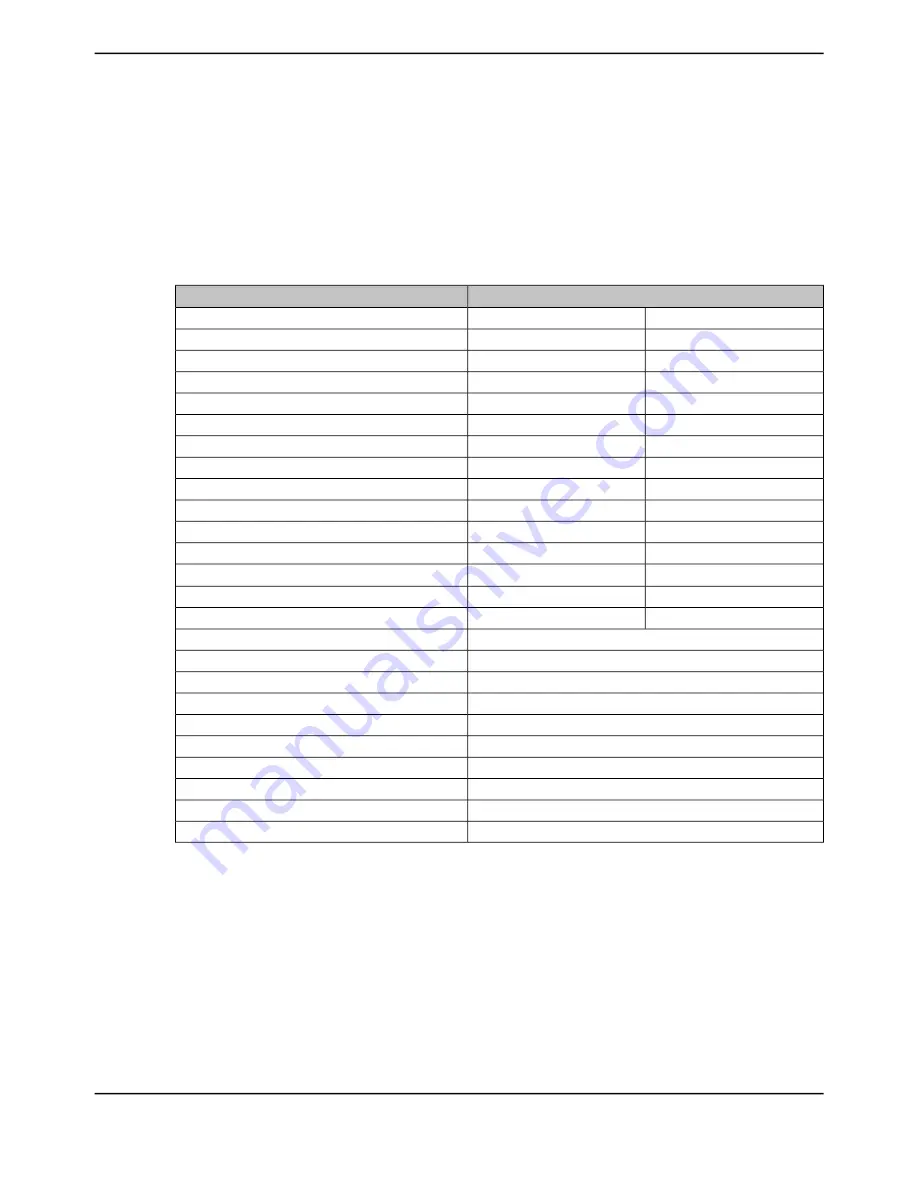

Table 11-3 on page 823 defines how EPI module signals should be connected to SDRAMs. The

table applies when using a x16 SDRAM up to 512 megabits. Note that the EPI signals must use

8-mA drive when interfacing to SDRAM, see page 774. Any unused EPI controller signals can be

used as GPIOs or another alternate function.

Table 11-3. EPI SDRAM x16 Signal Connections

SDRAM Signal

a

EPI Signal

D0

A0

EPI0S0

D1

A1

EPI0S1

D2

A2

EPI0S2

D3

A3

EPI0S3

D4

A4

EPI0S4

D5

A5

EPI0S5

D6

A6

EPI0S6

D7

A7

EPI0S7

D8

A8

EPI0S8

D9

A9

EPI0S9

D10

A10

EPI0S10

D11

A11

EPI0S11

D12

A12

b

EPI0S12

D13

BA0

EPI0S13

D14

BA1

EPI0S14

D15

EPI0S15

DQML

EPI0S16

DQMH

EPI0S17

CASn

EPI0S18

RASn

EPI0S19

not used

EPI0S20-EPI0S27

WEn

EPI0S28

CSn

EPI0S29

CKE

EPI0S30

CLK

EPI0S31

a. If two signals are listed, connect the EPI signal to both pins.

b. Only for 256/512 megabit SDRAMs.

11.4.2.2

Refresh Configuration

The refresh count is based on the external clock speed and the number of rows per bank as well

as the refresh period. The

RFSH

field represents how many external clock cycles remain before an

AUTO-REFRESH is required. The normal formula is:

RFSH

= (t

Refresh_us

/ number_rows) / ext_clock_period

A refresh period is normally 64 ms, or 64000 μs. The number of rows is normally 4096 or 8192. The

ext_clock_period is a value expressed in μsec and is derived by dividing 1000 by the clock speed

823

June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller