5 Nomenclature, Package Symbolization, and Revision Identification

The revision of the device can be identified by the revision letter on the

or by the

located inside the TLV structure of the device.

5.1 Device Nomenclature

To designate the stages in the product development cycle, TI assigns prefixes to the part numbers of all MSP

MCU devices. Each MSP MCU commercial family member has one of two prefixes: MSP or XMS. These

prefixes represent evolutionary stages of product development from engineering prototypes (XMS) through fully

qualified production devices (MSP).

XMS

– Experimental device that is not necessarily representative of the final device's electrical specifications

MSP

– Fully qualified production device

Support tool naming prefixes:

X

: Development-support product that has not yet completed Texas Instruments internal qualification testing.

null

: Fully-qualified development-support product.

XMS devices and X development-support tools are shipped against the following disclaimer:

"Developmental product is intended for internal evaluation purposes."

MSP devices have been characterized fully, and the quality and reliability of the device have been demonstrated

fully. TI's standard warranty applies.

Predictions show that prototype devices (XMS) have a greater failure rate than the standard production devices.

TI recommends that these devices not be used in any production system because their expected end-use failure

rate still is undefined. Only qualified production devices are to be used.

TI device nomenclature also includes a suffix with the device family name. This suffix indicates the temperature

range, package type, and distribution format.

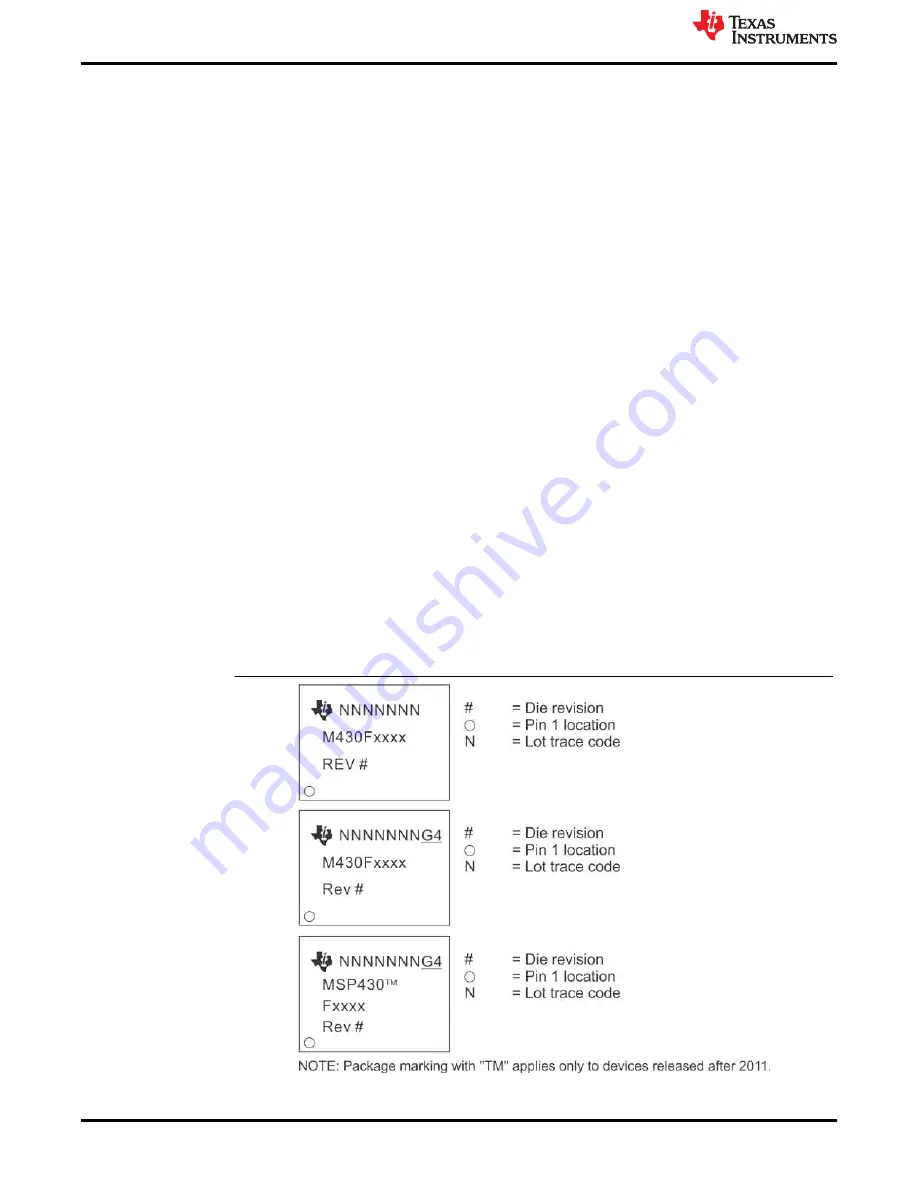

5.2 Package Markings

PZ100

LQFP (PZ) 100 Pin

Nomenclature, Package Symbolization, and Revision Identification

4

MSP430F6720A Microcontroller

SLAZ657S – FEBRUARY 2015 – REVISED MAY 2021

Copyright © 2021 Texas Instruments Incorporated