GUI Overview

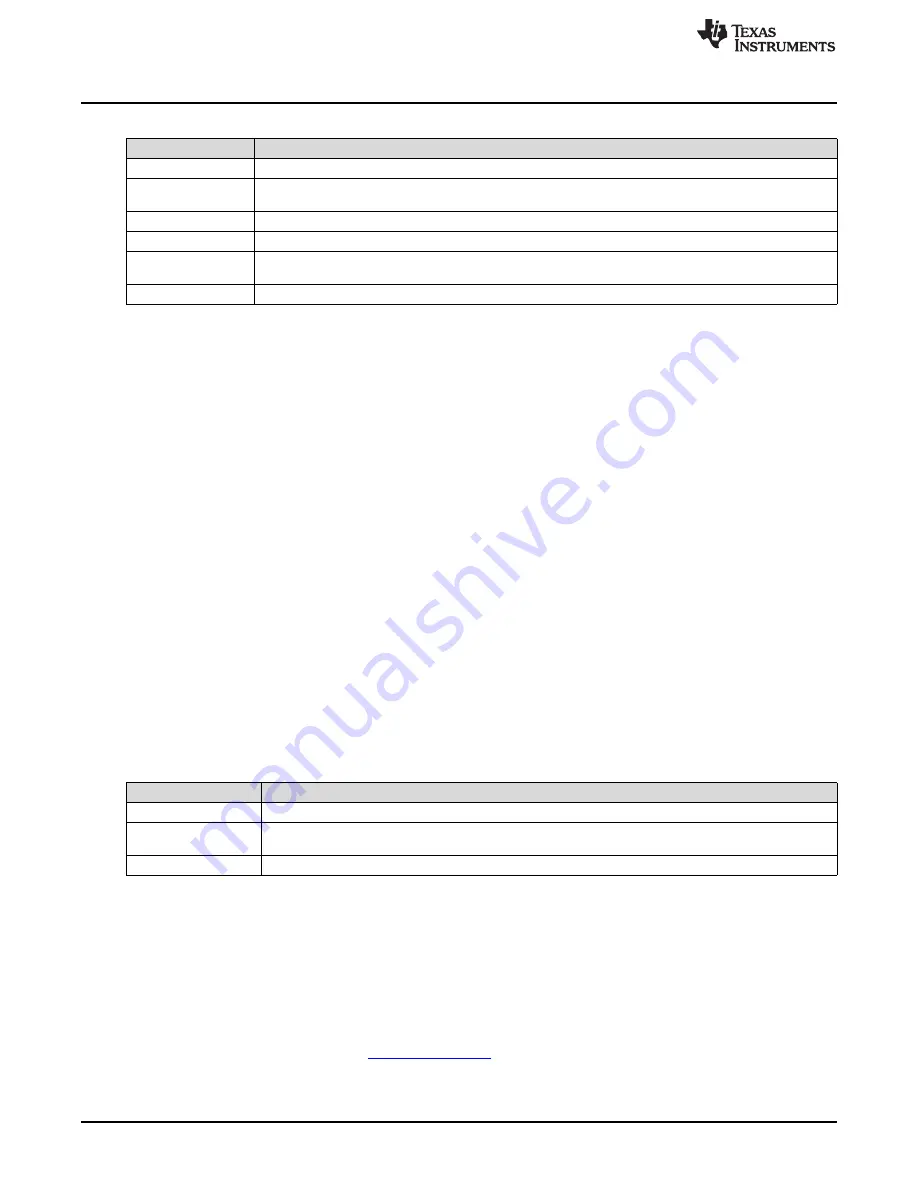

Table 1. Mode Information

Buck Mode

Disabled

Buck state machine in 'disable'

Soft Startup

Buck state machine in 'soft startup'. May occur when too much loading is present when powering-up the

buck.

PWM

Pulse Width Modulation

PFM

Pulse Frequency Modulation

ECO

PFM with 'low power coasting' mode enabled. This means that lots of analog resources are disabled

between PFM bursts. Reaction time to load transients is compromised, while Iq is minimized.

Sleeping

Multi-phase slave is passive.

The "Multi-phase Status" info field tells whether a buck core is configured as a master or slave. The field

also tells how many phases are active.

An ADC on the USB interface card is connected to measure the output voltage of the buck converter, and

this is displayed on GUI.

The "System Flags / Interrupts" section gives data on system faults and warnings. If the interrupt is set for

any reason the Interrupt active field shall show ‘1’ on red background. The flag causing the interrupt will

also be set on the Main tab. Interrupts on LP8754 can only be cleared by writing ‘0’ to associated

registers. Any individual flag can be cleared by clicking the Clear button next to each flag field. The USB

Interface Board uses an I

2

C-accessible temperature sensor IC to sense the EVB temperature near the

LP8754 IC. This information is presented in the "Board Temperature" field. LP8754 register 0x0D provides

a coarse temperature indication of the chip. This info is interpreted into the "Chip Temperature" field when

the "Poll Status" option is selected.

At the bottom of the GUI window is the "Auto Write" checkbox. If "Auto Write" is checked (default) any

checking, un-checking or pull-down menu selections will immediately launch I

2

C writes to the chip

register(s). If not checked, the user can update the chip registers to correspond the configuration selected

on the GUI by clicking "Write Registers".

If "Poll Status" is selected the software sends a query to the LP8754 at a fixed interval in order to detect

the status of the chip, including operation mode, multi-phase status, and output current. If not selected,

user can read the registers by applying "Read Registers". On the EVM both System I

2

C and DVS

(Dynamic Voltage Scaling) (that is, SmartReflex) buses can be used to interface the chip. The interface to

be used can be selected from the Interface pull-down menu. "Bus Speed" pull-down menu selections are

given in

below and are instantly applied for both buses. Notice that for DVS bus to work, NRST

needs to be high.

Table 2. I

2

C-Compatible Bus Support

Bus Speed Selection

Explanation

Fast (400 kHz)

Fast I

2

C-compliant operation at 400 kHz

Fast++ (3.4 MHz)

I

2

C protocol data transfer with 3.4 MHz clock rate. No writing of master code needed, but can done. Input

filters correspond to HS lengths – 10 ns minimum filter length for SCL and SDA:

High-Speed (3.4 MHz)

HS I

2

C-compliant data transfer with master codes.

3.2

Other Tabs and Menus

The "Tools" pull-down menu hosts another way of accessing the LP8754 registers. The "Direct Register

Access" tool can be used to read or write any register. When using direct register access, un-checking the

poll status checkbox is recommended. This way the GUI will only do the reads and writes commanded

from the direct access dialog.

The "Config" and "Advanced" tabs provide the user with pull-down menus and check-boxes for the part of

the register space that is not covered by the Main tab, such as output voltage control. These controls are

self-explanatory. Please refer to the

for explanation of the functions.

8

The LP8754 Evaluation Module

SNVU369 – August 2014

Copyright © 2014, Texas Instruments Incorporated