DAC and ADC GUI Configuration File Changes When Using a Xilinx

®

Development Platform

5

SLAU711 – March 2017

Copyright © 2017, Texas Instruments Incorporated

HSDC Pro With Xilinx

®

KCU105

5

DAC and ADC GUI Configuration File Changes When Using a Xilinx

®

Development

Platform

The configuration files that come with the TI ADC and DAC EVM GUIs are set up to operate with the

Altera

®

based, TI TSW14J56EVM. With the latest firmware, some GUIs can be configured as if they were

connected to the TSW14J56EVM. If that is not the case, then the EVM may be configured with Xilinx-

specified configuration files or a couple of changes to the settings of the LMK0482x registers. See

for details.

The firmware for the Xilinx Development Platforms use a separate clock input for REFCLK and core clock

to give maximum flexibility and support all line rates and subclasses with a single programmable design.

The Xilinx IP used in the firmware can be driven by a single clock in many circumstances (see the

clocking section of the Xilinx IP product guide for more details). THE REFCLK and core clock are

determined by the line rate conditions shown in

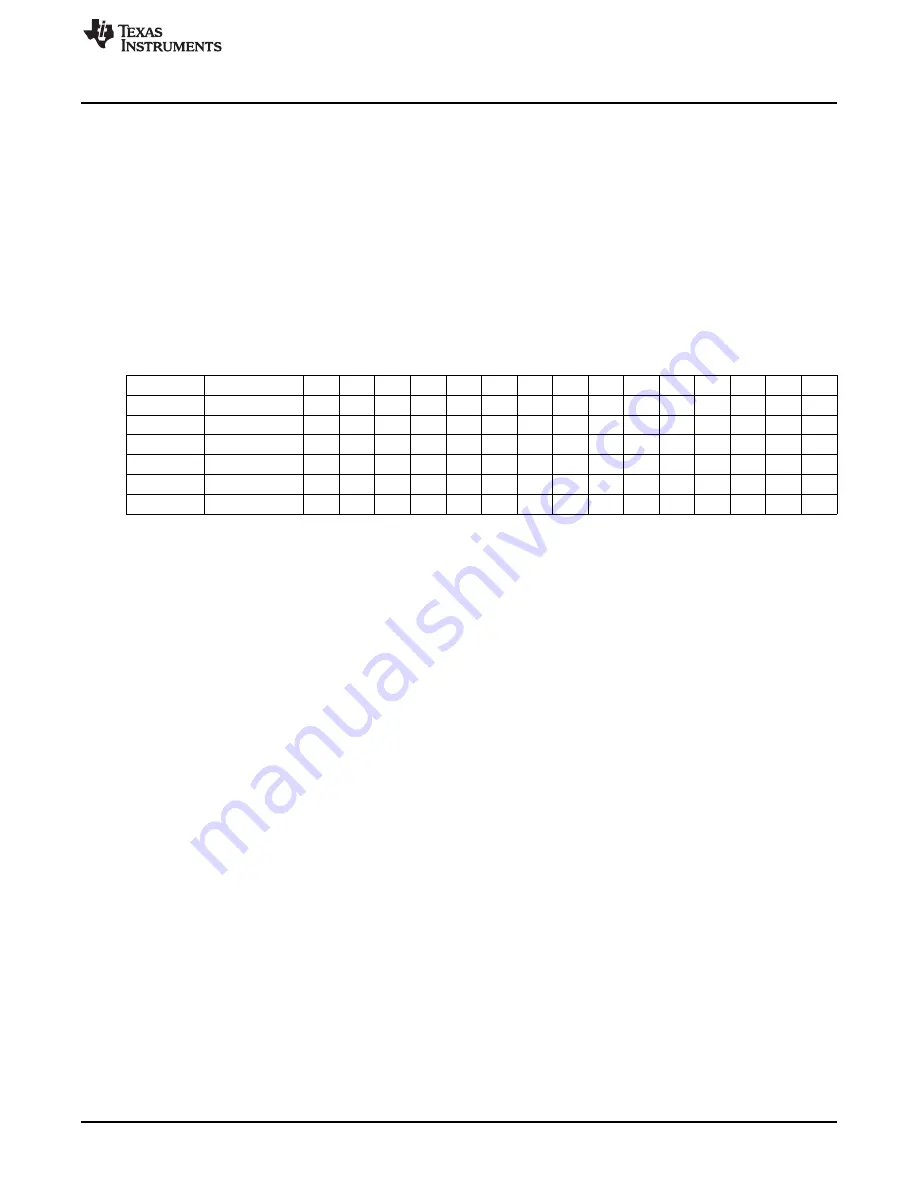

Table 1. Multiplier Line Rate Ranges

Max Lr (Gbps)

1.2

1.6

1.9

2

2.4

3.2

3.9

4

4.9

6.5

7.9

8.1

8.2

9.8

12.5

12.5

Min Lr (Gbps)

1

1.20

1.60

1.90

2.00

3.20

3.01

3.90

4.00

4.90

6.50

7.90

8.10

8.20

9.80

Multiplier

2

X

X

10

X

X

X

X

X

X

X

X

X

X

X

X

20

X

X

X

X

X

X

X

X

X

X

X

X

40

X

X

X

X

X

X

X

X

Line rate switching is supported across the entire speed range supported by transceivers. The ratio of

REFCLK to line rate multipliers is also programmable. The multiplier is programmed by the

.ini

files

located in HSDC Pro. Note: REFCLK = line rate / Multiplier

Example: A line rate of 5.0G is in the range between 4.90 Gbps and 6.5 Gbps and is supported by the

multiplier values of 10, 20, and 40. Therefore, the possible values for REFCLK are:

5.0G / 10 = 500 MHz, 5.0G / 20 = 250 MHz, 5.0G / 40 = 125 MHz