DAC Module

VCC

VSS

VCC

GND

GND

VDD

(J6 )

(P 6 )

(J3 )

SCLK

W4

VSS

SDI

(J4)

(P4)

(W9)

(W3)

(W12)

CS

VSS

± 5 VA

+ 3 .3 VD

FS

U4A

TP2

TP8

W8

LDAC

RST

+ 1 .8 VD

+ 3 .3 VA

U4B

TP1

+ 5 VA

W11

W1

+ 3 .3 VA

VCC + 5 VA

U2

TP3

SDO

(J2 )

(P 2 )

(W 6 )

(W 10 )

W5

REF5050

OPA277

V

H

REF

V

L

REF

IOV

DD

V

L

REF

V

H

REF

AV

DD

DV

DD

IOV

DD

V

OUT

R

FB

DGND

AGND

PCB Design and Performance

www.ti.com

The DAC output can be monitored through pins 2 and 6 of the J4 header connector. The DAC output can

be switched through the W2 jumper for stacking the EVM for daisy-chaining purposes.

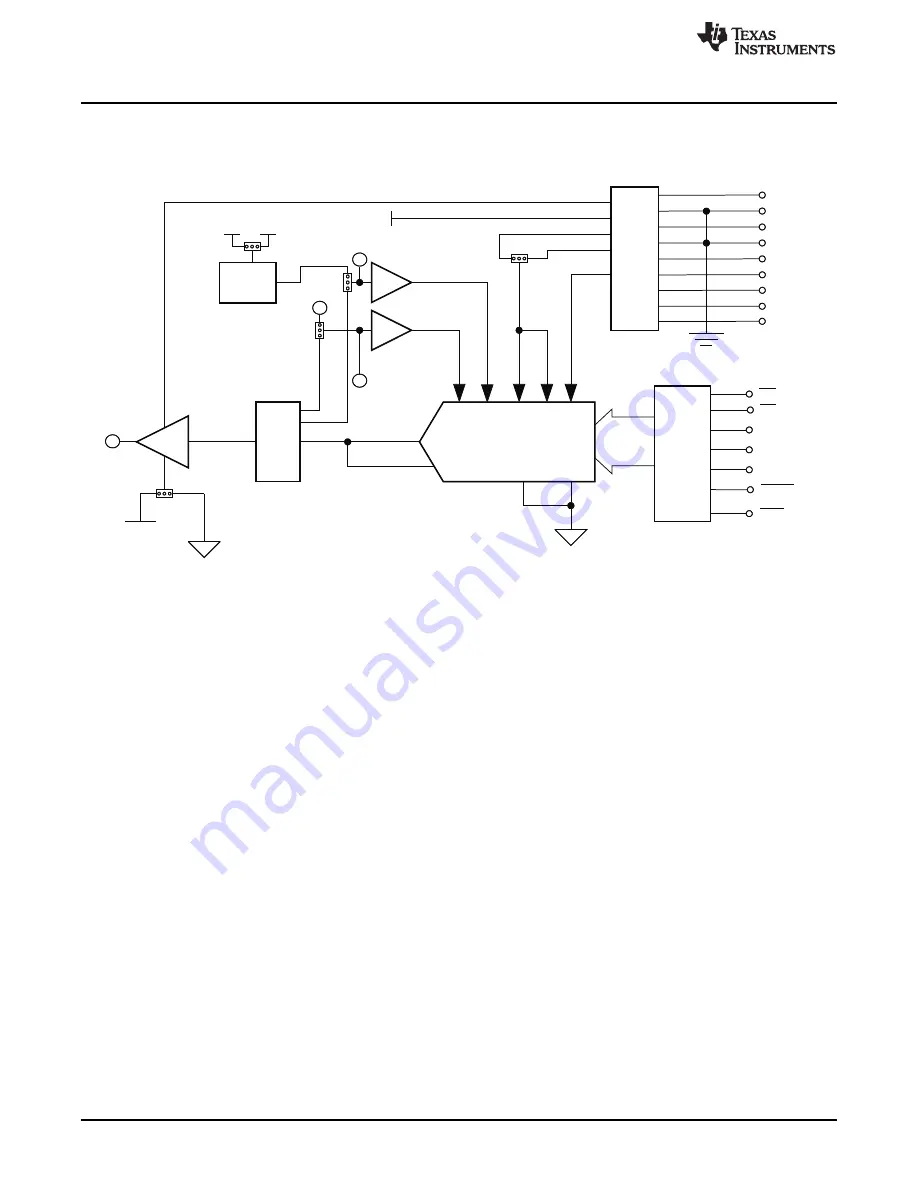

A block diagram of the EVM is shown in the

.

Figure 1. Block Diagram

2

PCB Design and Performance

This chapter describes the layout design of the PCB, the physical and mechanical characteristics of the

EVM, and the EVM test performance procedure performed. The list of components on this evaluation

module is also included in this section.

2.1

PCB Layout

The DAC8881 EVM is designed to preserve the performance quality of the DAC, device under test, as

specified in the datasheet. Carefully analyzing the physical restrictions of the EVM and the given or known

elements that contribute to performance degradation of the EVM is key to a successful design

implementation. These obvious attributes that diminish the performance of the EVM can be addressed

during the schematic design phase by selecting appropriate components and building a correct circuit. The

circuit should include adequate bypassing, identifying and managing analog and digital signals, and

knowing or understanding the mechanical attributes of the components.

The critical part of the design is the layout process. The main concern is primarily the placement of

components and the proper routing of signals. The bypass capacitors should be placed as close as

possible to the pins, and the analog and digital signals should be properly separated from each other. The

power and ground plane is very important and should be carefully considered in the layout process. A

solid plane is ideally preferred but sometimes impractical, so when a solid plane is not possible, a split

plane is an acceptable alternative. When considering a split plane design, analyze component placement

and carefully split the board into its analog and digital sections starting from the device under test. The

ground plane plays an important role in controlling noise and other effects that otherwise contribute to the

error of the DAC output. To ensure that the return currents are handled properly, route the appropriate

signals only in their respective sections, meaning the analog traces should only lay directly above or below

the analog section and the digital traces in the digital section. Minimize the length of the traces but use the

largest possible trace width allowable in the design. These design practices can be seen in the following

figures.

4

DAC8881 Evaluation Module

SLAU257A – September 2008 – Revised November 2009

Copyright © 2008–2009, Texas Instruments Incorporated