SPI Registers and Waveforms

964

SPRUH22I – April 2012 – Revised November 2019

Copyright © 2012–2019, Texas Instruments Incorporated

C28 Serial Peripheral Interface (SPI)

12.3 SPI Registers and Waveforms

This section contains the registers, bit descriptions, and waveforms.

12.3.1 SPI Control Registers

The SPI is controlled and accessed through registers in the control register file.

12.3.1.1 SPI Configuration Control Register (SPICCR)

SPICCR controls the setup of the SPI for operation.

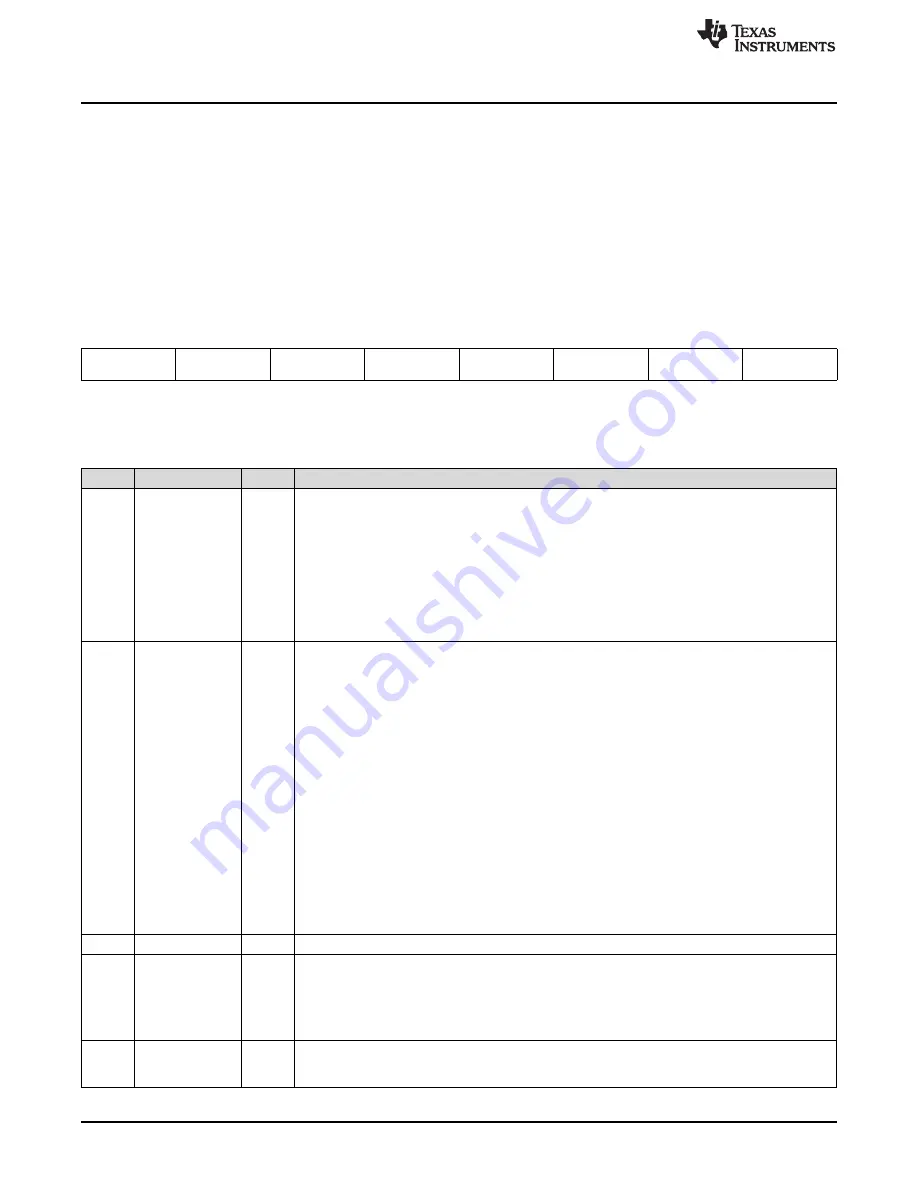

Figure 12-13. SPI Configuration Control Register (SPICCR) — Address 7040h

7

6

5

4

3

2

1

0

SPI SW Reset

CLOCK

POLARITY

Reserved

SPILBK

SPI CHAR3

SPI CHAR2

SPI CHAR1

SPI CHAR0

R/W-0

R/W-0

R-0

R-0

R/W-0

R/W-0

R/W-0

R/W-0

LEGEND: R/W = Read/Write; R = Read only; -

n

= value after reset

Table 12-8. SPI Configuration Control Register (SPICCR) Field Descriptions

Bit

Field

Value

Description

7

SPI SW RESET

SPI software reset. When changing configuration, you should clear this bit before making changes

and set this bit before resuming operation.

0

Initializes the SPI operating flags to the reset condition. Specifically, the RECEIVER OVERRUN

Flag bit (SPISTS.7), the SPI INT FLAG bit (SPISTS.6), and the TXBUF FULL Flag bit (SPISTS.5)

are cleared. SPISTE will become inactive. SPICLK will be immediately driven to 0 regardless of the

clock polarity. The SPI configuration remains unchanged.

1

SPI is ready to transmit or receive the next character. When the SPI SW RESET bit is a 0, a

character written to the transmitter will not be shifted out when this bit is set. A new character must

be written to the serial data register. SPICLK will be returned to its inactive state one SPICLK cycle

after this bit is set.

6

CLOCK

POLARITY

Shift Clock Polarity. This bit controls the polarity of the SPICLK signal. CLOCK POLARITY and

CLOCK PHASE (SPICTL.3) control four clocking schemes on the SPICLK pin. See

.

0

Data is output on rising edge and input on falling edge. When no SPI data is sent, SPICLK is at low

level. The data input and output edges depend on the value of the CLOCK PHASE bit (SPICTL.3)

as follows:

• CLOCK PHASE = 0: Data is output on the rising edge of the SPICLK signal; input data is latched

on the falling edge of the SPICLK signal.

• CLOCK PHASE = 1: Data is output one half-cycle before the first rising edge of the SPICLK

signal and on subsequent falling edges of the SPICLK signal; input data is latched on the rising

edge of the SPICLK signal.

1

Data is output on falling edge and input on rising edge. When no SPI data is sent, SPICLK is at

high level. The data input and output edges depend on the value of the CLOCK PHASE bit

(SPICTL.3) as follows:

• CLOCK PHASE = 0: Data is output on the falling edge of the SPICLK signal; input data is

latched on the rising edge of the SPICLK signal.

• CLOCK PHASE = 1: Data is output one half-cycle before the first falling edge of the SPICLK

signal and on subsequent rising edges of the SPICLK signal; input data is latched on the falling

edge of the SPICLK signal.

5

Reserved

Reads return zero; writes have no effect.

4

SPILBK

SPI loopback. Loop back mode allows module validation during device testing. This mode is valid

only in master mode of the SPI.

0

SPI loop back mode disabled – default value after reset

1

SPI loop back mode enabled, SIMO/SOMI lines are connected internally. Used for module self

tests.

3-0

SPI CHAR3

−

SPI CHAR0

Character Length Control Bits 3-0. These four bits determine the number of bits to be shifted in or

out as a single character during one shift sequence.

lists the character length selected

by the bit values.