8 bytes

Underflow

margin

FIFO_THR=13

TXFIFO

SWRS037B – JANUARY 2006 – REVISED MARCH 2015

Table 5-7. FIFO_THR Settings

and the Corresponding FIFO

Thresholds (continued)

BYTES in TX

FIFO_THR

FIFO

0111

33

1000

29

1001

25

1010

21

1011

17

1100

13

1101

9

1110

5

1111

1

The chip status byte that is available on the SO pin while transferring the SPI address contains the fill

grade of the TX FIFO.

contains more details on this.

The number of bytes in the TX FIFO can also be read from the TXBYTES.NUM_TXBYTES status register.

The 4-bit FIFOTHR.FIFO_THR setting is used to program the FIFO threshold point.

lists the 16

FIFO_THR settings and the corresponding thresholds for the TX FIFO.

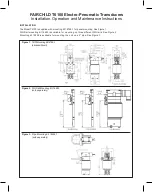

Figure 5-14. Example of FIFO at Threshold

A flag will assert when the number of bytes in the FIFO is equal to or higher than the programmed

threshold. The flag is used to generate the FIFO status signals that can be viewed on the GDO pins (see

shows the number of bytes in the TX FIFO when the threshold flag toggles, in the case of

FIFO_THR=13.

shows the flag as the FIFO is filled above the threshold, and then drained

below.

30

Detailed Description

Copyright © 2006–2015, Texas Instruments Incorporated

Product Folder Links:

Содержание CC1150

Страница 61: ...PACKAGE OPTION ADDENDUM www ti com 30 May 2018 Addendum Page 2 ...

Страница 64: ......

Страница 65: ......