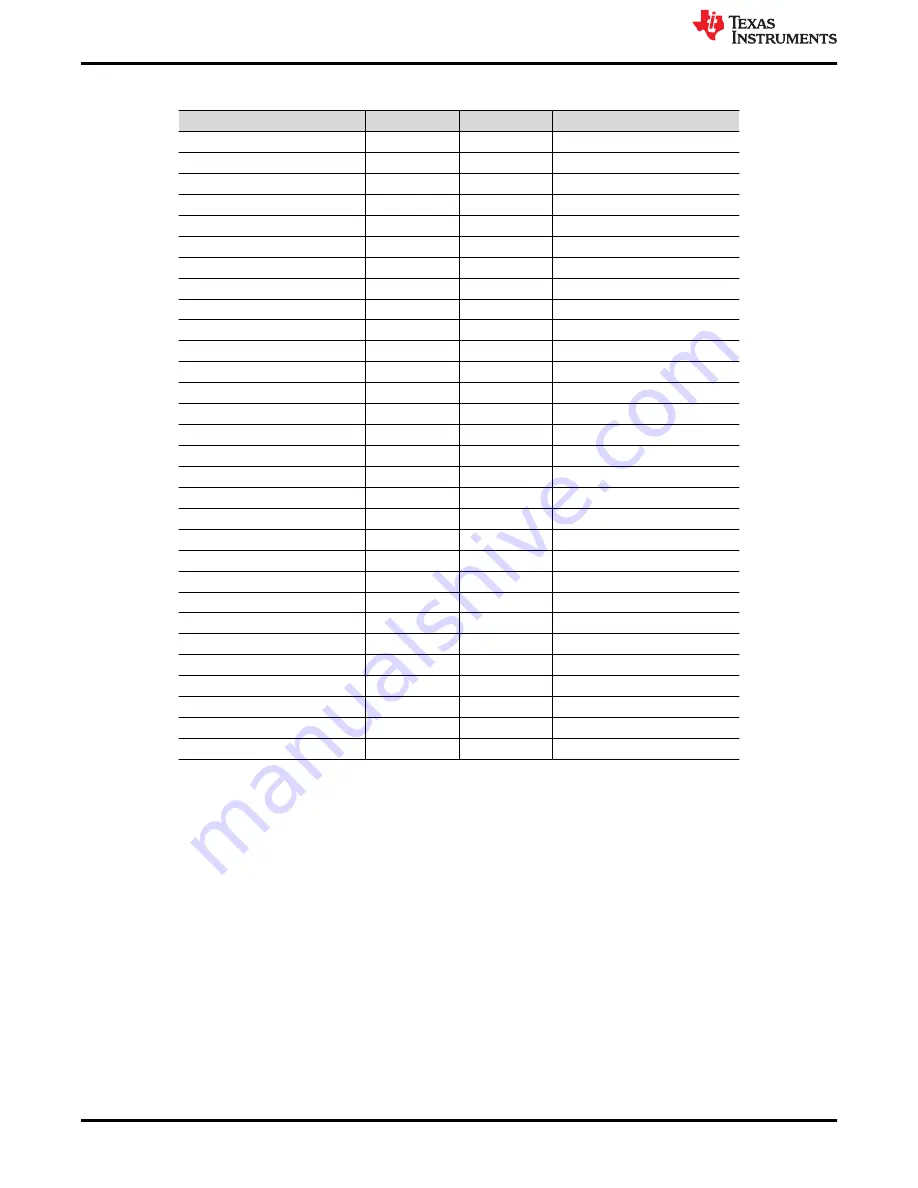

Table 3-2. ADC-PHI-PRU-EVM Parallel Mode QSH Connector Signal Routing to

the AM64x and AM24x

Signal Name

Pin Number

Pin Number

Signal Name

5V

2

1

5.5V

5V

4

3

DGND

PRU0_GPIO15

6

5

—

PRU0_GPIO14

8

7

—

PRU0_GPIO13

10

9

—

PRU0_GPIO12

12

11

—

PRU0_GPIO11

14

13

—

PRU0_GPIO10

16

15

—

PRU0_GPIO9

18

17

—

PRU0_GPIO8

20

19

—

PRU0_GPIO7_LATCH_IN1

22

21

—

PRU0_GPIO6

24

23

PRU0_GPIO16

PRU0_GPIO5

26

25

—

PRU0_GPIO4

28

27

—

PRU0_GPIO3

30

29

HSE_GPIO0_42

PRU0_GPIO17_SYNC_OUT1

32

31

PRU0_GPIO18_LATCH_IN0

—

34

33

HSE_GPIO0_35

PRU0_GPIO19_SYNC_OUT0

36

35

—

PRU0_GPIO2

38

37

HSE_GPIO0_29

PRU0_GPIO1

40

39

HSE_GPIO0_24

PRU0_GPIO0

42

41

HSE_GPIO0_44

PRU1_GPIO17_SYNC_OUT1

44

43

PRU1_GPIO7

Jumper to 44/MCU GPIO

46

45

PRU1_GPIO9

PRU1_GPIO10

48

47

—

DVDD

50

49

HSE_GPIO0_32

PRU1_GPIO14

52

51

HSE_GPIO0_34

PRU1_GPIO16

54

53

HSE_GPIO0_37

SOC_I2C0_SDA

56

55

HSE_GPIO0_39

SOC_I2C0_SCL

58

57

HSE_GPIO0_41

DGND

60

59

ID PWR

ADC-PHI-PRU-EVM Circuitry

8

ADC-PHI-PRU-EVM Evaluation Module

SBAU396 – MAY 2022

Copyright © 2022 Texas Instruments Incorporated