T3903

Page 6 of 21

Document Number: DS-000358

Revision: 1.0

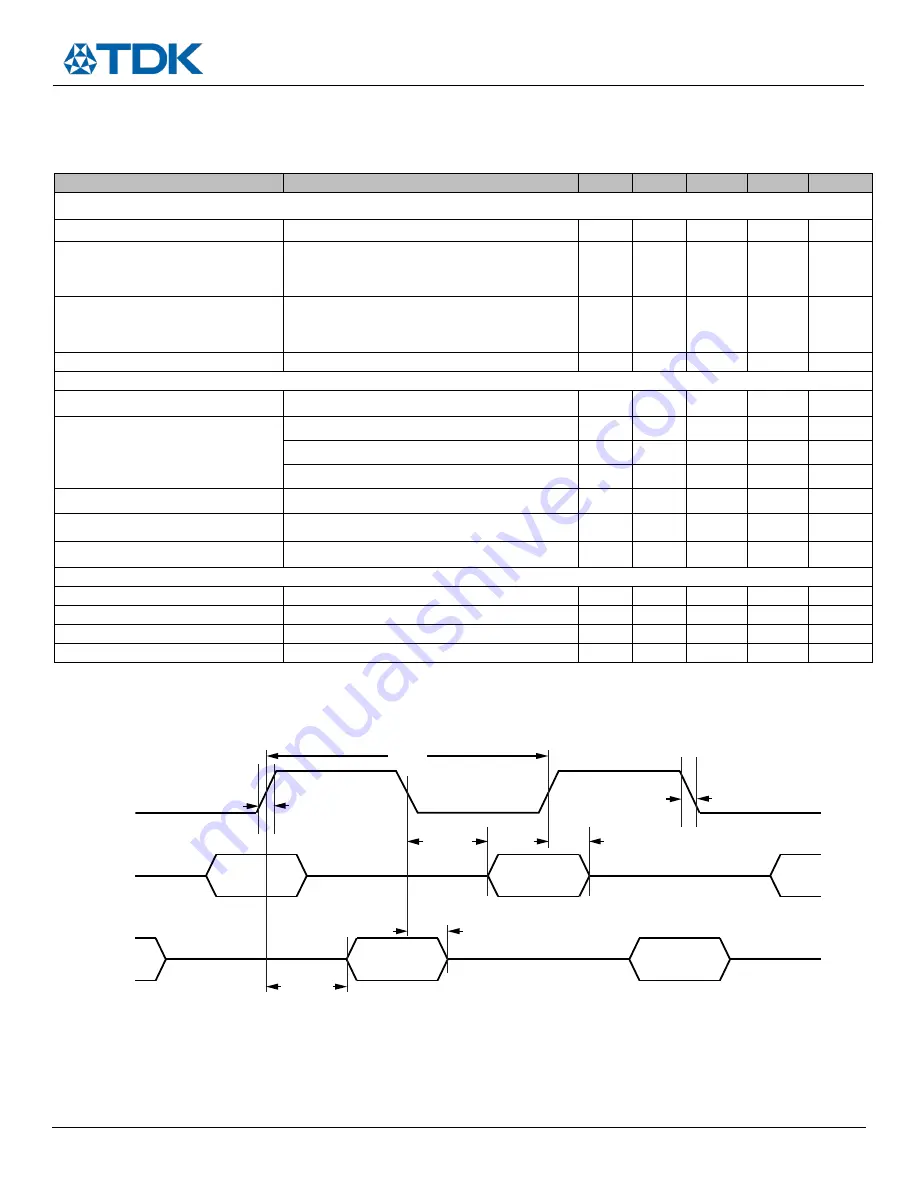

TABLE 5. PDM DIGITAL INPUT/OUTPUT

T

A

= 25

°C,

1.8 V

< VDD < 3.3 V

, unless otherwise noted.

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS NOTES

MODE SWITCHING

Sleep Time

Time from f

CLK

falling <200 kHz

1

ms

Wake-Up Time

High Quality mode, Sleep Mode to f

CLK

>1.2

MHz, output within 0.5 dB of final sensitivity,

power on

7

ms

Wake-Up Time

Low-Power Mode, Sleep Mode to f

CLK

>400

kHz, output within 0.5 dB of final sensitivity,

power on

7

ms

Switching time

Between Low-Power and High Quality Mode

7

ms

INPUT

t

CLKIN

Input clock period

303

2500

ns

Clock Frequency (CLK)

Sleep Mode

200

kHz

Low-Power Mode

400

800

kHz

High Quality Mode

2.0

3.3

MHz

Clock Duty Cycle

f

CLK

<3.3 MHz

45

55

%

t

RISE

CLK rise time (10% to 90% level)

25

ns

4

t

FALL

CLK fall time (90% to 10% level)

25

ns

4

OUTPUT

t

1OUTEN

DATA1 (right) driven after falling clock edge

30

ns

t

1OUTDIS

DATA1 (right) disabled after rising clock edge

5

18

ns

t

2OUTEN

DATA2 (left) driven after rising clock edge

30

ns

t

2OUTDIS

DATA2 (left) disabled after falling clock edge

5

18

ns

Note 4:

Guaranteed by design

TIMING DIAGRAM

Figure 1. Pulse Density Modulated Output Timing

t

CLKIN

CLK

DATA2

DATA1

t

2OUTDIS

t

1OUTDIS

t

2OUTEN

t

1OUTEN

t

RISE

t

FALL