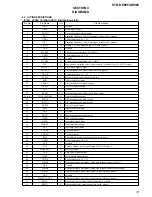

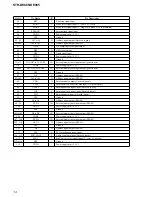

14

STR-DE885/DE985

56

BST

I

Boot stop signal input

57

MOD1

I

Mode select signal input (L : 384fs, H : 256fs)

58

MOD0

I

Mode select signal input (L : single chip mode, H : use prohibited)

59

EXLOCK

I

External lock signal input

60

VDDI

—

Power supply pin (+2.5 V)

61

VSS

—

Ground

62, 63

A17, A16

O

Address signal output (Not used (open))

64 to 66

A15 to A13

O

Address signal output (SRAM)

67

GP10

O

L/R sampling clock signal output

68

GP9

O

GP9 signal output

69

GP8

I

Audio signal input

70

VDDI

—

Power supply pin (+2.5 V)

71

VSS

—

Ground

72 to 75

D15/GP7 to D12/GP4

I/O

External memory data input/output (general port)

76

VDDE

—

Power supply pin (+3.3 V)

77 to 80

D11/GP3 to D8/GP0

I/O

External memory data input/output (general port)

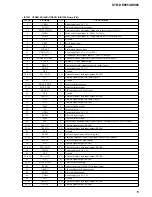

81

VSS

—

Ground

82

A9

O

Address signal output (SRAM)

83 to 85

A12 to A10

O

Address signal output (SRAM)

86

TDO

O

Emulation data output (Not used (open))

87

TMS

I

Emulation start/end select data input (Not used (open))

88

XTRST

I

Emulation break signal input (Not used (open))

89

TCK

I

Emulation clock signal input (Not used (open))

90

TDI

I

Emulation data input (Not used (open))

91

VSS

—

Ground

92 to 97

A8 to A3

O

Address signal output (SRAM)

98, 99

D7, D6

I/O

External memory data input/output (SRAM)

100

VDDI

—

Power supply pin (+2.5 V)

101

VSS

—

Ground

102 to 105

D5 to D2

I/O

External memory data input/output (SRAM)

106

VDDE

—

Power supply pin (+3.3 V)

107, 108

D1, D0

I/O

External memory data input/output (SRAM)

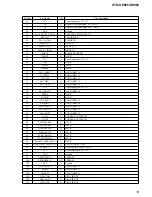

109, 110

A2, A1

O

Address signal output (SRAM)

111

VSS

—

Ground

112

A0

O

Address signal output (SRAM)

113

PM

I

PLL initialization signal input

114, 115

SDI3, SDI4

I

Audio serial data input (Not used (open))

116

SYNC

I

Sync/unsync select signal input (L : sync, H : unsync)

117 to 119

VSS

—

Ground

120

VDDI

—

Power supply pin (+2.5 V)

Pin No.

Pin Name

I/O

Pin Description

Содержание STR-DE885

Страница 12: ...12 STR DE885 DE985 MEMO ...