74

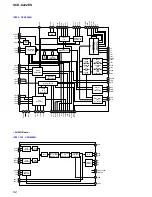

SCD-C222ES

•

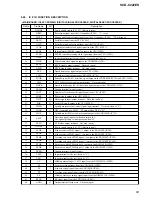

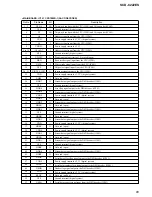

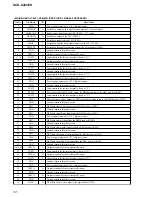

MAIN BOARD IC901 CXP974096-001R (CPU)

Pin No.

Pin Name

I/O

Description

1

MODE DF

O

SACD/CD mode selection signal output to the muting circuit

“L”: CD mode, “H”: SACD mode

2

AMUTE

O

Muting on/off signal output to the analog line circuit “L”: muting on

3

DOCTRL

O

Digital out on/off control signal output to the CXD3068Q (IC509)

“L”: digital out off, “H”: digital out on

4

LAT DAC

O

Serial data latch pulse signal output to the D/A converter Not used (open)

5

DATA DAC

O

Serial data output to the D/A converter Not used (open)

6

CLK DAC

O

Serial data transfer clock signal output to the D/A converter Not used (open)

7

FCS JMP 1

O

Focus jump 1 signal output to the BA5983FP (IC502)

8

FCS JMP 2

O

Focus jump 2 signal output to the BA5983FP (IC502)

9

SENS CD

I

Internal status (SENSE) signal input from the CXD3068Q (IC509)

10

XCS DRAM

O

Chip select signal output to the D-RAM Not used (pull up)

11

XCS IO

O

Chip select signal output to the I/O expander (IC902)

12

XCS DVD

O

Chip select signal output to the CXD1882R (IC701)

13

VSS

—

Ground terminal (digital system)

14 to 21

D0 to D7

I/O

Two-way data bus with the CXD1882R (IC701) and I/O expander (IC902)

22

INT0 DVD

I

Interrupt signal input from the CXD1882R (IC701)

23

INT1 DVD

I

Interrupt signal input from the CXD1882R (IC701)

24

T SENS

I

Disc tray status detection signal input from the table sensor (D10)

25

MON DVD

I

Monitor signal input terminal Not used (open)

26

DATA CD

O

Serial data output to the CXD3068Q (IC509)

27

XLAT CD

O

Serial data latch pulse signal output to the CXD3068Q (IC509)

28

A1IN

I

Sircs remote control signal input of the CONTROL A1II (J381)

29

COUT CD

I

Numbers of track counted signal input from the CXD3068Q (IC509)

30

IN SW

I

Loading in switch input terminal “L”: loading in Not used (fixed at “H”)

31

OUT SW

I

Loading out switch input terminal “L”: loading out Not used (fixed at “H”)

32

MIRR RF

I

Mirror signal input from the CXD3068Q (IC509)

33

SUBQ CD

I

Subcode Q data input from the CXD3068Q (IC509)

34

SCOR CD

I

Subcode sync (S0+S1) detection signal input from the CXD3068Q (IC509)

35

SQCLK CD

O

Subcode Q data reading clock signal output to the CXD3068Q (IC509)

36

—

—

Not used (open)

37

CLOK CD

O

Serial data transfer clock signal output to the CXD3068Q (IC509)

38

XRST

I

System reset signal input from the reset signal generator (IC905) “L”: reset

For several hundreds msec. after the power supply rises, “L” is input, then it changes to “H”

39

VSS

—

Ground terminal (digital system)

40

XTAL I

System clock input terminal (20 MHz)

41

EXTAL O

System clock output terminal (20 MHz)

42

VDD

—

Power supply terminal (+3.3V) (digital system)

43

SPDA

O

Spindle motor (M3) control signal output to the BA5912AFP (IC512)

44

APDO

O

Output terminal for offset adjustment of APEO (

<z/.

pin of CXD1882R (IC701))

45

MUTE DSD

O

Muting on/off signal output to the DSD decoder (IC801) and CXD9647R (IC803)

“H”: muting on

46

XMSLAT

O

Serial data latch pulse signal output to the DSD decoder (IC801)

47

READY DSD

I

Ready signal input from the DSD decoder (IC801) and CXD9647R (IC803) “L”: ready

48

SDIN DSD

I

Serial data input from the DSD decoder (IC801) and CXD9647R (IC803)

49

SOUT DSD

O

Serial data output to the DSD decoder (IC801) and CXD9647R (IC803)