– 29 –

•

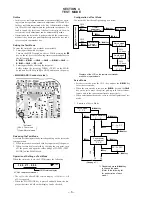

MAIN BOARD IC601 CXD2663GA

Pin No.

Pin Name

I/O

Description

1

VDCO

—

Power supply terminal (+2V) (for internal logic)

2

MNT0

O

Signal indicating the speed follow-up spinning mode output to the system controller (IC801)

“H”: speed follow-up spinning mode

3

MNT1

O

Sled motor operation monitor signal output to the system controller (IC801) “H”: monitor drive

4

MNT2

O

Speed limiter signal output to the system controller (IC801) “L”: limiter on

5

MNT3

O

Window signal to detect an inverse trigger edge output to the system controller (IC801)

“H”: edge detectable

6

SWDT

I

Writing data input from the system controller (IC801)

7

SCLK

I

Serial clock signal input from the system controller (IC801)

8

XLAT

I

Serial data latch pulse input from the system controller (IC801)

9

VSCO

—

Ground terminal (for internal logic)

10

SRDT

O

Reading data output to the system controller (IC801)

11

SENS

O

Internal status (SENSE) output to the system controller (IC801)

12

XRST

I

System reset signal input from the MPC1830ADTB (IC901) “L”: reset

For several hundreds msec. after the power supply rises, “L” is input, then it changes to “H”

13

SQSY

O

Subcode Q sync (SCOR) output the system controller (IC801)

“L”: is output every 13.3 msec Almost all, “H” is output

14

MTFLGL

O

Muting applied to analog signal input in non-signal status causes the signal to be “H”

automatically Not used

15

TST1

I

Input terminal for the test (fixed at “L”)

16

XINT

O

Interrupt status output to the system controller (IC801)

17

TST2

I

Input terminal for the test (fixed at “L”)

18

VDIOSC

—

Power supply terminal (+2.4V) (for oscillator cell)

19

OSCI

I

System clock (512Fs=22.5792 MHz) input terminal

20

OSCO

O

System clock (512Fs=22.5792 MHz) output terminal

21

VSIOSC

—

Ground terminal (for oscillator cell)

22

DAVSSL

—

Ground terminal (for internal D/A converter L-ch)

23

VREFL

O

Reference voltage output terminal (for internal D/A converter L-ch)

24

AOUTL

O

Playback analog signal (L) output to the headphone amplifier (IC301)

25

DAVDDL

—

Power supply terminal (+2.4V) (for internal D/A converter L-ch)

26

DAVDDR

—

Power supply terminal (+2.4V) (for internal D/A converter R-ch)

27

AOUTR

O

Playback analog signal (R) output to the headphone amplifier (IC301)

28

VREFR

O

Reference voltage output terminal (for internal D/A converter R-ch)

29

DAVSSR

—

Ground terminal (for internal D/A converter R-ch)

30

VSC1

—

Ground terminal (for internal logic)

31

XTSL

I

Input terminal for the system clock frequency setting

“L”: 45.1584 MHz, “H”: 22.5792 MHz (fixed at “H” in this set)

32, 33

TST3, TST4

I

Input terminal for the test (normally : fixed at “L”)

34

DOUT

O

Digital audio signal output terminal when playback mode Not used (open)

35

DT72

O

Not used (open)

36, 37

VDC1, VDC2

—

Power supply terminal (+2V) (for internal logic)

38

DATAI

I

Input terminal of external audio data to the internal D/A converter Not used (open)

39 to 41

TST5 to TST7

I

Input terminal for the test (normally : fixed at “L”)

42

DADT

O

Playback data signal output to the external D/A converter Not used (open)

(DIGITAL SIGNAL PROCESSOR, DIGITAL SERVO SIGNAL PROCESSOR, EFM/ACIRC ENCODER/DECODER,

SHOCK PROOF MEMORY CONTROLLER, ATRAC ENCODER/DECODER, D/A CONVERTER, 16M BIT D-RAM)

Содержание MZ-E80

Страница 12: ......