69

•

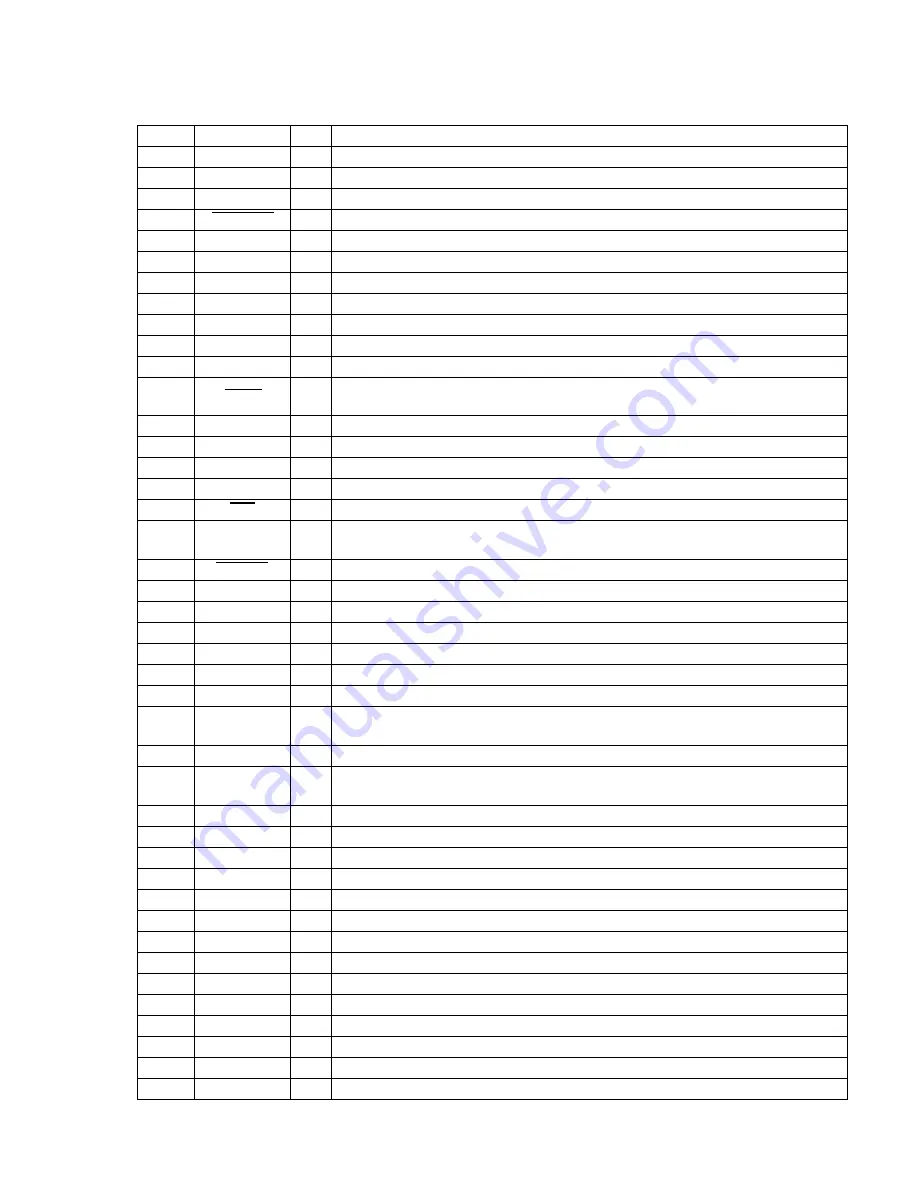

MAIN BOARD IC601 M30624MG-A10FP (SYSTEM CONTROLLER (MD MECHANISM CONTROLLER))

Pin No.

Pin Name

I/O

Description

1

DACDTI

O

Serial data output to the A/D, D/A converter (IC401)

2

DACCLK

O

Serial data transfer clock signal output to the A/D, D/A converter (IC401)

3

DALATCH

O

Serial data latch pulse signal output to the A/D, D/A converter (IC401)

4

DARESET

O

Reset signal output to the A/D, D/A converter (IC401) “L”: reset

5

XAMUTE

O

Audio line muting on/off control signal output terminal “L”: line muting on

6

SIRCS

I

Remote control signal input from the remote control receiver (IC781)

7

NC

O

Not used (open)

8

BYTE

I

External data bus line byte selection signal input “L”: 16 bit, “H”: 8 bit (fixed at “L”)

9

CNVSS

—

Ground terminal

10

XCIN

I

Sub system clock input terminal (32.768 kHz) Not used (pull down)

11

XCOUT

O

Sub system clock output terminal (32.768 kHz) Not used (open)

12

S.RST

I

System reset signal input from the M62016L (IC906) “L”: reset

For several hundreds msec. after the power supply rises, “L” is input, then it changes to “H”

13

XOUT

O

Main system clock output terminal (10 MHz)

14

GND

—

Ground terminal

15

XIN

I

Main system clock input terminal (10 MHz)

16

VCC

—

Power supply terminal (+3.3V)

17

NMI

I

Non-maskable interrupt input terminal “L” active (fixed at “H” in this set)

18

DQSY

I

Digital In U-bit CD format subcode Q sync (SCOR) input from the CXD2656AR (IC121)

“L” is input every 13.3 msec Almost all, “H” is input

19

P.DOWN

I

Power down detection signal input terminal “L”: power down, normally: “H”

20

SOFT RST

I

Software reset signal input terminal Not used (pull up)

21

JOGCD0

I

Jog dial pulse input from the rotary encoder (S701

l

AMS

L

) A phase input

22

JOGCD1

I

Jog dial pulse input from the rotary encoder (S701

l

AMS

L

) B phase input

23

JOGMD0

I

Jog dial pulse input from the rotary encoder (S721

l

AMS

L

) A phase input

24

JOGMD1

I

Jog dial pulse input from the rotary encoder (S721

l

AMS

L

) B phase input

25, 26

NC

O

Not used (open)

27

SQSY

I

Subcode Q sync (SCOR) input from the CXD2656AR (IC121)

“L” is input every 13.3 msec Almost all, “H” is input

28

I2CBUSY

I/O

Not used (open)

29

I2CCLK

I/O

Communication data reading clock signal output or transfer clock signal input with the CD

mechanism controller (IC501)

30

I2CDATA

I/O

Communication data bus with the CD mechanism controller (IC501)

31

SWDT

O

Writing data output to the CXD2656AR (IC121)

32

SRDT

I

Reading data input from the CXD2656AR (IC121)

33

SCLK

O

Serial clock signal output to the CXD2656AR (IC121)

34

FLCS

O

Chip select signal output to the FL/LED driver (IC751)

35

FLDATA

O

Serial data output to the FL/LED driver (IC751)

36

NC

O

Not used (open)

37

FLCLK

O

Serial data transfer clock signal output to the FL/LED driver (IC751)

38 to 43

NC

O

Not used (open)

44

LINE SEL2

O

Audio line selection output terminal

45

LINE SEL1

O

Audio line selection output terminal

46

LINE SEL0

O

Audio line selection output terminal

47, 48

NC

O

Not used (open)

49

STB

O

Strobe signal output to the power supply circuit “L”: standby mode, “H”: power on