41

41

HCD-FX900W

HCD-FX900W

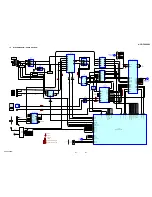

7-4. BLOCK DIAGRAM – AUDIO SECTION –

: AUDIO

• Signal Path

: AUDIO IN

: DIGITAL IN(OPTICAL IN)

: DIGITAL IN(COAXIAL IN)

: TUNER

IC401

AMP

+

–

6

5

7

+

–

3

2

1

Q470-473,476

MO/ST DETECT

IC372

AMP

+

–

2

3

1

GAIN CONT

DC CONT

MO/ST DET

PLUG DET1

Q474,475

GAIN CONT

MUTING

Q300,310,320

IC350

AUDIO INPUT SELECTOR

IC351

AUDIO INPUT SELECTOR

IC102

DIAT CONTROLLLER

4 Y3

2 Y2

5 Y1

13

X

3

Y

1 Y0

A

A SEL1

A SEL0

10

B

9

11 X3

15 X2

L-CH

R-CH

14 X1

12 X0

Q395

Q396

Q397

IC360

AMP

+

–

3

2

1

+

–

5

6

7

LIN

RIN

12 X0

3

Y

A

1 Y0

14 X1

5 Y1

13

X

22 COMTXM

COMRXM

19

23 COMTXP

COMRXP

18

39

41

12SSCLK

37 12SDATA

43 12SDCLK

12SLRCLK

IRQ

10

82 A-SEL0

83 A-SEL1

69 TUNED

TUNED

70 ST_CLK

PLL CK

PLL DO

PLL CE

PLL DI

71 ST_DO

72 ST_CE

73 ST_DI

91 A-SEL2

26 MIC GAIN

28 DC CONT

90 MONO/ST DET

100 MIC/A CALSW

A SEL2

GAIN CONT

MO/ST DET

PLUG DET1

79 V_SEL0

80 V_SEL1

84 V_SEL2

81 TVSEL/V_SEL3

AV_SEL0

AV_SEL1

AV_SEL2

AV_SEL3

J203

TV/VCR1

TV/VCR1

TUNER

SECTION

J401

AUDIO IN/

L-CH

+4V

-D

+D

R-CH

L

L

R

R

TUNED

MCK

LRCK

BCK

DATA

RESET

RESET

X101

45.1584MHz

SCTXOUT

SCRXIN

ERR_IRQ

RX_IN

TX_OUT

PLL CK

PLL DO

PLL CE

PLL DI

D

VIDEO

SECTION

(Page 39)

D433

D470

DC CONT

29

30

I2C CLK

I2C CLK

I2C DATA

I2C DATA

3

4

CN502

SOFT JIG

TV/VCR2

TV/VCR2

L

R

L

R

L

L

L

R

L

R

R

R

J101

X M

5

9

3

11

OSCIN

OSCOUT

26

28

(2/2)

A.CAL MIC

AM

FM

75

COAXIAL

Ω

AUDIO IN

4

3

2

1

IC702

DIGITAL AUDIO

INTERFACE

14

BCK

15

LRCK

36

DI

35

DO

38

CL

37

CE

25

CFALAG

48

XSTATE

DIR_HDOUT

DIR_CLK

DIR_HCE

CS FLAG

DIR_RST

34

ERROR

24

AUDIO

79 DAI_P12

DAI_P19

DAI_P18

D2

D3

94 DAI_P20

81

80

DAI-P13

DAI-P14

89

88

13 CKOUT

A

B

Y

4 DIN1

5 DIN2

X701

12.288MHz

22

21

XIN

XOUT

X1

25MHz

CLKIN

143

142

XTAL

15 FLAG1

86

DAI_P16

DAI_P17

DAI_P20

87

94

64

DSPOA

65

DSPOB

70

DSPOC

SPICLK

RESET

MISO

LRCKO

BCKO

MCK

D1

D3

D2

IC302

INVERTER

IC771

AND GATE

IC701

A/D CONVERTER

IC2

DIGITAL AUDIO PROCESSOR

2

DOUT

1

MCLK

3

LRCK

19 AINL

IC704

SELECTOR

LRCK0

10

1

3B

A/B

9

3Y

7

2Y

4

1Y

12

4Y

11 3A

BCKO

6 2B

5 2A

D1

MCK0

3 1B

2 1A

14 4A

13 4B

IC671

SELECTOR

11

4Y

8

3Y

6

2Y

3

1Y

12 4A

9 3A

5 2A

2 1A

16 AINR

2

4

2

4

6

BCLK

7

PDWN

17

XSTATE

126

121

125

16 FLAG1

97 FLAG2

78 DSPIA

127 HDIN

16

DATA

DIR_ZERO

DIR_DATA

DIN

DIN

DIR_HDOUT

DIR_CLK

DIR_CLK

DIR_HCE

XSTATE

DIR_RST

CSFLAG

DIR_RERR

DIR_RERR

DIR_ZERO

1

72

AD RST

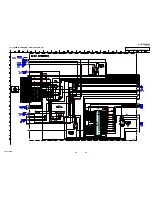

IC501 (2/4)

SYSTEM CONTROLLER

5

DSP DIN/DIR DIN

3

DSP INTR

122 SPIDS

56

DSP_SPIDS

63

DIR HDOUT

7

DSP DIN/DIR CLK

59

DIR HCE

61

DIR XSTATE

TX_OUTT

RX_IN

ERR_IRQ

RESET

35 36

XM_SC_RX_IN

XM_SC_TX_OUT

75

XM_ERR_IRQ

77

XM_RESET

57

SEL_SA_CD

58

DIR RST

6

DSP_MISO

55

DSP_RESET

19

DIR_CSFLAG

60

DIR_RERR

18

DIR_ZORO

58

DIR_RST

LRCKO

BCKO

D1

D2

D3

MCKO

IC301

OPTICAL

J302

OUT

1

OPTICAL

DIGITAL IN

COAXIAL IN

BCK

MCK

LRCK

DATA

IN

RF SECTION

AMP SECTION

(Page 38)

(Page 40)

A

E