DVP-S533D

3-7

3-8

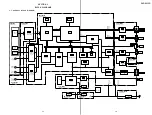

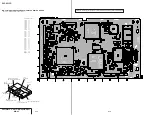

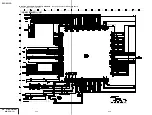

3-4. SYSTEM CONTROL BLOCK DIAGRAM

MB-85 BOARD(3/6)

(SEE PAGE 4-29, 31, 33)

23 XECS

24 XEWC

25 XEBSY

HGA

IC601

BUFFER

IC203

4K EEPROM

IC201

SYSTEM CONTROL

IC202

141

142

145

144

143

157

156

155

114

115

116

117

118

135

102

103

104

105

106

107

108

109

110

111

HINT1

HINT3

3

98

99

CPUCK

10

7

22

23

11

SC0

SO0

SI0

24

19

94

88

RDY

INT1

INT3

83

CLK

MUTE

MD2

NORF

DFCT

FWON

LOCK

VS

SI0

HD 0-15

HA 0-21

SIO

SO0

SC0

SI1

SO1

SC1

XFRRST

CS0L

HA 1-16

HD 0-15

D 16-31

A 01-15

HD 8-15

XIFINT

HA 0-5, 17-19

HD 0-7

HA 0-5, 17-19

SO0

SC0

SI1

SO1

SC1

PB1

MUTE

MD2

NORF

DFCT

FWON

LOCK

72

71

VS

53

59

XRD

XWRH

XCS2

XCS3

XAVDIT

9

8

95

84

85

86

INT0

DACK1

DACK0

DREQ1

87

DREQ0

DACK1

DACK0

DREQ1

DREQ0

MCK

XDACS0

XDACS1

P66

PB4

CKSEL

DVD/CD

PB2

27M30

N27MSDP

X001

27MHz

27M01

384FSDA

384FS01

33M30

256FS30

33MARP

4

112

113

124

125

3

76 77 78 79 80 89

14 97

X1

X201

12.5MHz

X0

GAIN2

HD 8-15

HA 0, 1

HD 0-15

HA 0-21

X3VRST

91

42 44-64

25-39 41

1

19

66 100

99 98

1

3

5

3

6

1

4

3

5

8

6

1

12

22

11

4

6

1

3

FCSON

XSDPRST

XSDPIT

XSDPWR

XSDPRD

XSDPCS

SPDLSTOP

54

57

SPGAIN

XDRVMUTE

XVIFCS

IFSC0

IFSO0

4A

2A

1A

4Y

2Y

1Y

SC1

SO1

SI1

SC1

SO1

SI1

CS0L

SC0

SO0

SI0

XFRRST

IFSI0

XFRRST

XIFINT

LDMP/DMP

LDMM/DMM

OCSW1

OCSW2

CKSW1

FCSON

SPDLSTOP

SPGAIN

XDRVMUTE

LDMP/DMP

LDMM/DMM

OCSW1

OCSW2

CKSW1

94

93

92

91

64

63

88

X01INT0

X01INT1

X01CS

29

30

28

XDACS2

XDACS3

X01RST

XDACRST

MA MUTE

96

97

XDACS2

XDACS3

MA MUTE

31

26

49

126-133

146-154

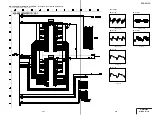

PLL

IC001

IC003

IC004

N27MHGA

RF, SERVO

(SEE PAGE 3-4)

SIGNAL PROCESS,

VIDEO

(SEE PAGE 3-5)

AUDIO 2

(SEE PAGE 3-11)

AUDIO 2

(SEE PAGE 3-11)

RST

PB7

PB3

CS2

CS3

CE

CS

WE

RD

WR0

WR1

PF7

CS4

CS1

CS0

MD

ML

XT1

05

SCKO2

SCKO1

SCKO3

16M FLASH

IC206

1M SRAM

IC204

CS, WE,

OE, UB, LB

WE, UB, LB,

RY/BY, OE

HA 1-20

HD 0-15

WE, RY/BY,

OE, CE

DI

DO

SK

WC

CS

R/B

4

5

CS1

CS4

HRD

HWRH

HWRL

WAIT

RST

ARPRST

ARPINT

ARPWT

ARPWR

ARPRD

ARPCS

AVDWT

AVDRST

XARPRST

XARPIT

XARPWT

XARPWR

XARPRD

XARPCS

XAVDWT

XAVDRST

01IT0

01IT1

01CS

01RST

DACRST

SDPRST

SDPIT

SDPWR

SDPRD

SDPCS

INTERFACE

CONTROL

(SEE PAGE 3-14)

RF, SERVO

(SEE PAGE 3-4)

RF, SERVO

(SEE PAGE 3-4)

AUDIO 1

(SEE PAGE 3-9)

AUDIO 1

(SEE PAGE 3-9)

AUDIO 1

(SEE PAGE 3-9)

SIGNAL PROCESS,

VIDEO

(SEE PAGE 3-5)

SIGNAL PROCESS,

VIDEO

(SEE PAGE 3-5)

SIGNAL PROCESS,

VIDEO

(SEE PAGE 3-5)

POWER ON

RESET

IC207

+3.3V

2.4Vp-p(12.5MHz)

IC202

(™

DVD:6.2Vp-p(37.0MHz)

CD:5Vp-p(33.6MHz)

IC003

5

,

7

92

4Vp-p(25.3MHz)

IC202

5

5

4.2Vp-p(26.9MHz)

IC004

2

,

5

,

7

5

2

7

7

4.2Vp-p(27.0MHz)

IC001

6

6

DVD:5.8Vp-p(36.5MHz)

CD:5.1Vp-p(33.8MHz)

IC001

!¶

4.2Vp-p(25.3MHz)

IC001

!¢

(DVD play)

4.7Vp-p(22.5MHz)

IC001

!¢

(CDplay)

4.6Vp-p(33.8MHz)

IC001

!™

12

17

14

Содержание DVP-S533

Страница 6: ...1 1 SECTION 1 GENERAL This section is extracted from in struction manual 3 867 038 11 DVP S533D ...

Страница 7: ...1 2 ...

Страница 8: ...1 3 ...

Страница 9: ...1 4 ...

Страница 10: ...1 5 ...

Страница 11: ...1 6 ...

Страница 12: ...1 7 ...

Страница 13: ...1 8 ...

Страница 14: ...1 9 ...

Страница 15: ...1 10 ...

Страница 16: ...1 11 ...

Страница 17: ...1 12 ...

Страница 18: ...1 13 ...

Страница 19: ...1 14 1 14 E ...

Страница 23: ...2 4 2 11 INTERNAL VIEW DC motor loading 1 541 632 11 Optical pick up KHM 220AAA J1RP 8 820 081 03 ...

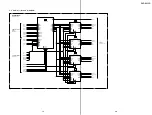

Страница 34: ...DVP S533D 4 3 4 4 4 1 FRAME SCHEMATIC DIAGRAM FRAME 1 SCHEMATIC DIAGRAM FRAME 1 2 ...

Страница 35: ...DVP S533D FRAME 2 SCHEMATIC DIAGRAM 4 5 4 6 FRAME 2 2 ...

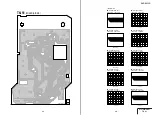

Страница 53: ...DVP S533D 4 41 4 42 AU 212 AUDIO SCHEMATIC DIAGRAM Ref No AU 212 board 2 000 series AUDIO AU 212 1 2 ...