SN32F260 Series

32-Bit Cortex-M0 Micro-Controller

SONiX TECHNOLOGY CO., LTD

Page 77

Version 1.5

PWM1 is 0 when TC<MR1 during Up-counting period.

01: PWM mode 2.

PWM1 is 1 when TC<MR1 during Up-counting period.

10: PWM1 is forced to 0.

11: PWM1 is forced to 1.

1:0

PWM0MODE[1:0]

PWM0 output.

00: PWM mode 1.

PWM0 is 0 when TC<MR0 during Up-counting period.

01: PWM mode 2.

PWM0 is 1 when TC<MR0 during Up-counting period.

10: PWM0 is forced to 0.

11: PWM0 is forced to 1.

R/W

0

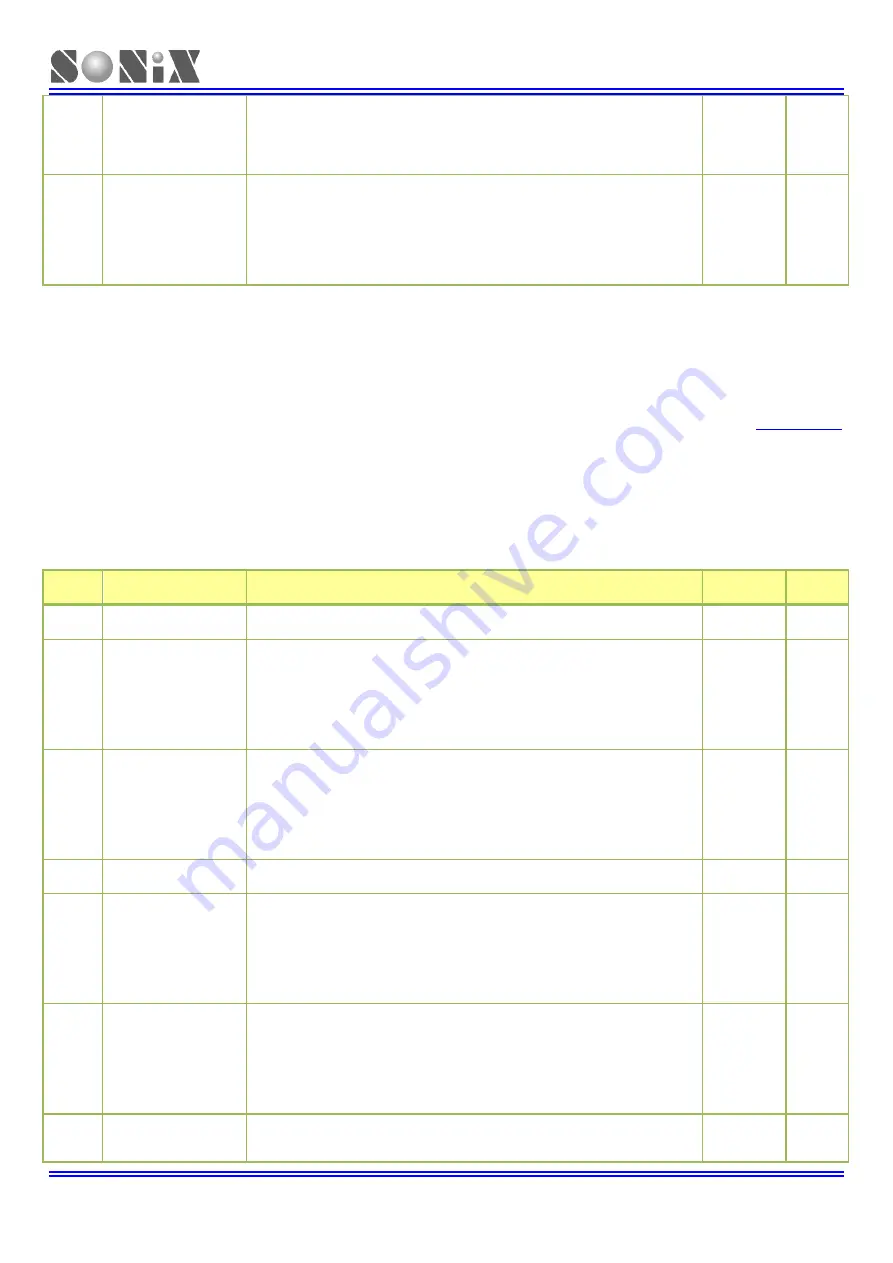

6.7.18 CT16Bn PWM Control register 2 (CT16Bn_PWMCTRL2) (n=1)

Address Offset: 0x98

The PWM Control register is used to configure the match outputs as PWM outputs. Each match output can be

in-dependently set to perform either as PWM output or as match output whose function is controlled by

register.

For each timer, a maximum of 4 single edge controlled PWM outputs can be selected on the CT16Bn_PWMCTRL [3:0]

outputs. One additional match register determines the PWM cycle length. When a match occurs in any of the other

match registers, the PWM output is set to HIGH. The timer is reset by the match register that is configured to set the

PWM cycle length. When the timer is reset to zero, all currently HIGH match outputs configured as PWM outputs are

cleared.

Bit

Name

Description

Attribute

Reset

31:14

Reserved

R

0

13:12

PWM22MODE[1:0]

PWM22 output.

00: PWM mode 1.

PWM22 is 0 when TC<MR22 during Up-counting period.

01: PWM mode 2.

PWM22 is 1 when TC<MR22 during Up-counting period.

10: PWM22 is forced to 0.

11: PWM22 is forced to 1.

R/W

0

11:10

PWM21MODE[1:0]

PWM21 output.

00: PWM mode 1.

PWM21 is 0 when TC<MR21 during Up-counting period.

01: PWM mode 2.

PWM21 is 1 when TC<MR21 during Up-counting period.

10: PWM21 is forced to 0.

11: PWM21 is forced to 1.

R/W

0

9:8

Reserved

R

0

7:6

PWM19MODE[1:0]

PWM19 output.

00: PWM mode 1.

PWM19 is 0 when TC<MR19 during Up-counting period.

01: PWM mode 2.

PWM19 is 1 when TC<MR19 during Up-counting period.

10: PWM19 is forced to 0.

11: PWM19 is forced to 1.

R/W

0

5:4

PWM18MODE[1:0]

PWM18 output.

00: PWM mode 1.

PWM18 is 0 when TC<MR18 during Up-counting period.

01: PWM mode 2.

PWM18 is 1 when TC<MR18 during Up-counting period.

10: PWM18 is forced to 0.

11: PWM18 is forced to 1.

R/W

0

3:2

PWM17MODE[1:0]

PWM17 output.

00: PWM mode 1.

PWM17 is 0 when TC<MR17 during Up-counting period.

R/W

0

Содержание SN32F260 Series

Страница 132: ...SN32F260 Series 32 Bit Cortex M0 Micro Controller SONiX TECHNOLOGY CO LTD Page 132 Version 1 5 16 2 QFN 46 PIN ...

Страница 136: ...SN32F260 Series 32 Bit Cortex M0 Micro Controller SONiX TECHNOLOGY CO LTD Page 136 Version 1 5 16 6 QFN 33 PIN ...

Страница 137: ...SN32F260 Series 32 Bit Cortex M0 Micro Controller SONiX TECHNOLOGY CO LTD Page 137 Version 1 5 16 7 SSOP 24 PIN ...