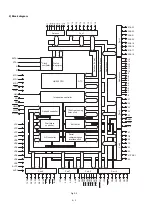

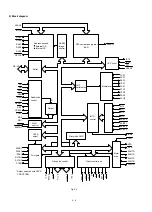

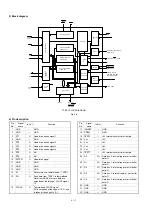

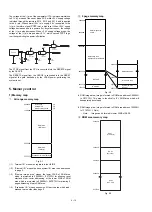

3) Block diagram

TPRC1 BLOCK DIAGRAM

Fig. 2-8

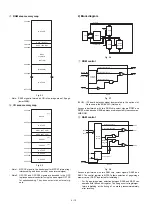

4) Pin description

MOTOR

CONTROL

HEAD

I/F

MISC.

TEST

CIRCUIT

CUTTER

CONTROL

PB I/F UNIT

SYSTEM

I/F

PORT

PDCTLU

DECODEK UNIT

HEAD CONTROL

TIMER UNIT

MOTOR CONTROL

TIMER UNIT

CUTTER CONTROL

TIMER UNIT

CLOCK

GEN.

IN

T

E

RRUP

T

CI

RC

U

IT

H

O

ST

BU

S

I/

F

U

N

IT

INHBEC

CSEN

CGS

RD,WR

A0~23

D0~7

WO

WI

INT

INTI

PHAI

(

Φ)

BD0~7

BA0~15

BRAS,BRAS

BRD,BWR

RES

POF,INH

POP,PHUP,PFP,PCRES

PTRM,PTJM

CLOCK,SO,ST1~5,HCO

SI

EBAK,EPEQ

EBRK,EACK

RVPON,JVPON,

RAS,RBS,RCS,RDS,

JAS,JBD,JCS,JDS

TEST1,TEST2

CTAO,CTBO

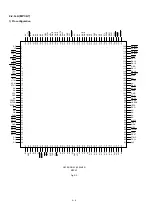

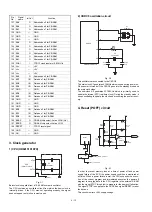

Pin

No.

Signal

name

In/Out

Function

1

GND

—

GND

2

GND

—

GND

3

ST1

O

Head drive strobe signal 1

4

GND

—

GND

5

ST2

O

Head drive strobe signal 2

6

ST3

O

Head drive strobe signal 3

7

ST4

O

Head drive strobe signal 4

8

ST5

O

NU

9

ST6

O

NU

10

LATCH

O

Head latch signal

11

GND

—

GND

12

GND

—

GND

13

GND

—

GND

14

SI

I

Data return line, thermalhead -- TPRC1

15

SO

O

Send data from TPRC1 to thermalhead

Data from PB-RAM or zero data are

outputted at the falling of CLOCK signal.

16

16

CLOCK

O

Thermalhead CLOCK signal

SO is outputted at the edge of I Ä O, and

is taken at the edge of o Ä I.

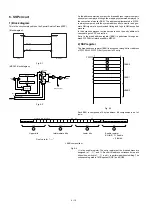

Pin

No.

Signal

name

In/Out

Function

17

INHDEC

I

GND

18

CSEN

I

GND

19

TEST2

I

+5V internal counter timer test pin

20

Vcc

—

+5V

21

Vcc

—

+5V

22

Vcc

—

+5V

23

Vcc

—

+5V

24

TEST1

I

+5V internal counter timer test pin

25

D0

I/O

Data bus 0: Internal register, print buffer

data IO

26

D1

I/O

Data bus 1: Internal register, print buffer

data IO

27

D2

I/O

Data bus 2: Internal register, print buffer

data IO

28

D3

I/O

DAta bus 3: Internal register, print buffer

data IO

29

D4

I/O

Data bus 4: Internal register, print buffer

data IO

30

GND

—

GND

31

GND

—

GND

32

GND

—

GND

4 – 11

Содержание ER-A450

Страница 51: ...MAIN PWB LAYOUT 1 SIDE A 8 15 ...

Страница 52: ... 2 SIDE B 8 16 ...

Страница 53: ...PS PWB FRONT DISPLAY PWB POP UP DISPLAY PWB 8 17 ...