- 15 -

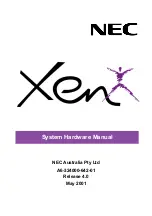

IC BLOCK DIAGRAM & DESCRIPTION

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

S48/PG0

S49/PG1

S50/PG2

S51/PG3

P00

P01

P02

P03

VSS2

VDD2

P04

P05

P06

P07

P10/SO0

P11/SI0/SB0

P12/SCK0

P13/SO1

P14/SI1/SB1

P15/SCK1

S19/PC3

S18/PC2

S17/PC1

S16/PC0

VDD3

S15/T15

S14/T14

S13/T13

S12/T12

S11/T11

S10/T10

S9/T9

S8/T8

S7/T7

S6/T6

S5/T5

S4/T4

S3/T3

S2/T2

S1/T1

S47/P

F

7

S46/P

F

6

S45/P

F

5

S44/

PF4

S43/P

F

3

S42/P

F

2

S41/P

F

1

S40/P

F

0

VDD4

S39/PE7

S38/PE6

S37/PE5

S36/PE4

S35/PE3

S34/PE2

S33/PE1

S32/PE0

S31/P

D

7

S30/P

D

6

S29/P

D

5

S28/P

D

4

S27/P

D

3

S26/P

D

2

S25/P

D

1

S24/P

D

0

S23/P

C

7

S22/

PC6

S21/P

C

5

S20/P

C

4

VP

P16/BUZZ

P17/P

W

M

0

P30

P31

P32

P33

P34

P35

P36

P37

P70/I

N

T

0

RES

XT

1/P74

XT

2/P75

VSS1

CF1

CF2

VDD1

P80/A

N

0

P81/A

N

1

P82/A

N

2

P83/A

N

3

P84/A

N

4

P85/A

N

5

P86/A

N

6

P87/A

N

7

P71/IN

T

1

7

2/IN

T

2/T

0

IN

0

I

P72/IN

T

3/T N

S0/T0

IC601 LC866540A-51D1 (Micro Processor)

NO.

PIN NAME

NAME

I/O

DESCRIPTION

1

P16/BUZ

JOG+

I

Input JogDial

2

P17/PWM0

JOG-

I

Input JogDial

3

P30

D_CLK

O Serial clock output for Tu/Vol_Func IC

4

P31

D_OUT

O Serial date output for Tu/Vol_Func IC

5

P32

O Open

6

P33

O Open

7

P34

O Open

8

P35

VF_CE

O Serial latch output for Vol_Func IC

9

P36

TU_CE

O Serial latch output for Tu IC

10

P37

TU_D1

I

Serial date input for Tu IC

11

P70/INT0

PROTECTOR

I

Protect Set (High; Irregular)

12

RES

RESET

I

System Reset pin

13

XT1/P74

XT1

I

Sub clock junction pin

14

XT2/P75

XT2

O Sub clock junction pin

15

XSS1

VSS

16

CF1

CF1

I

Main clock junction pin

17

CF2

CF2

O Main clock junction pin

18

VDD1

VDD

19

P80/AN0

KEY0

I

20

P81/AN1

KEY1

I

21

P82/AN2

SW0

I

CD; Limit SW, Open SW, Close SW

22

P83/AN3

I

Connect to GND

23

P84/AN4

I

Connect to GND

24

P85/AN5

I

Connect to GND

25

P86/AN6

I

Connect to GND

26

P87/AN7

I

Connect to GND

27

P71/INT1

WRQ

I

CD DSP interface(sub Q Request)

28

P72/INT2/T0IN

RDS IN

I

Serial date input for RDS IC

29

P73/INT3/T0IN

IR

I

Remote control input

30

S0/T0

O Open

31

S1/T1

O Open

32

S2/T2

O Open

33

S3/T3

O Open

34

S4/T4

O Open

35

S5/T5

O Open

36

S6/T6

O FL digit output (10G)

37

S7/T7

O FL digit output (9G)

38

S8/T8

O FL digit output (8G)

39

S9/T9

O FL digit output (7G)

40

S10/T10

O FL digit output (6G)

41

S11/T11

O FL digit output (5G)

42

S12/T12

O FL digit output (4G)

43

S13/T13

O FL digit output (3G)

44

S14/T14

O FL digit output (2G)

45

S15/T15

O FL digit output (1G)

46

VDD3

VDD

47

S16/PC0

O FL Segment output (P17)

48

S17/PC1

O FL Segment output (P16)

49

S18/PC2

O FL Segment output (P15)

50

S19/PC3

O FL Segment output (P14)

NO.

PIN NAME

NAME

I/O

DESCRIPTION

51

VP

VP

FL drive output power

52

S20/PC4

O FL Segment output (P13)

53

S21/PC5

O FL Segment output (P12)

54

S22/PC6

O FL Segment output (P11)

55

S23/PC7

O FL Segment output (P10)

56

S24/PD0

O FL Segment output (P9)

57

S25/PD1

O FL Segment output (P8)

58

S26/PD2

O FL Segment output (P7)

59

S27/PD3

O FL Segment output (P6)

60

S28/PD4

O FL Segment output (P5)

61

S29/PD5

O FL Segment output (P4)

62

S30/PD6

O FL Segment output (P3)

63

S31/PD7

O FL Segment output (P2)

64

S32/PE0

O FL Segment output (P1)

65

S33/PE1

O Open

66

S34/PE2

O Open

67

S35/PE3

SEL_POE_RY

I

Power Relay Function Select (High; None)

68

S36/PE4

V_CHK

I

Detection for Power Failure (Low; Power Failure)

69

S37/PE5

C2F

I

DSP C2F input

70

S38/PE6

REEL

I

Reel Rotor Signal Input

71

S39/PE7

I

Connect to GND

72

VDD4

VDD

Power(+5V)

73

S40/PF0

G_REVS

I

Failure record SW (Tape B side) Input

74

S41/PF1

G_FWD

I

Failure record SW (Tape A side) Input

75

S42/PF2

PACK

I

Tape Pack Check Input

76

S43/PF3

TAPE_INI

I

Tape Deck Initialize

77

S44/PF4

POW_RY

O Power Relay Control Output (High; Relay On)

78

S45/PF5

SP_RY

O Speaker Relay Control Output (High; Relay On)

79

S46/PF6

LED

O Light for CD

80

S47/PF7

Moter

O Tape Moter Output (High; Moter On)

81

S48/PG0

Tape Play PL

O Tape Play Plunger Output (High; Plunger On)

82

S49/PG1

P_CON

O Power control (High; Power On)

83

S50/PG2

OSC

O Control for Oscillation of Tape On/Off (High; Oscillation)

84

S51/PG3

PRE_MUTE

O Pre Amp Mute Output (High; Mute On)

85

P00

MAIN_MUTE

O Power Amp Mute Output (Low; Mute on)

86

P01

SURROUND

O Surround Output Open

87

P02

DSP_RESET

O Reset Signal for CD DSP

88

P03

CLK_SHIFT

O Main clock shift

89

VSS2

VSS

Power (GND)

90

VDD2

VDD

Power (+5V)

91

P04

BEAT

O Beat CCL Control

92

P05

R_Mute

O Tape Recording Mute (High; Mute On)

93

P06

TRY_OPEN

O Trey Open Control Output

94

P07

TRY_CLOSE

O TREY Close Control Output

95

P10/S00

COIN

O CD_DSP interface(command data output)

96

P11/S10/SB0

SQOUT

I

CD_DSP interface(SubQ data input)

97

P12/SCK0

CQCK

O CD_DSP interface(clock)

98

P13/S01

VD_GND

O GND control output for micon power check

99

P14/S11/SB1

DRF

I

DRF signal input

100

P15/SCK1

RWC

O CD_DSP interface(command latch)