Samsung Electronics

7-3

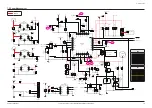

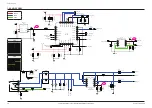

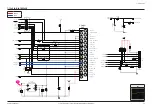

Schematic Diagram

This Document can not be used without Samsung’s authorization.

7-3 MAIN CPU-2

PBA_CE

LCD_RED2

JTAG_TCK

LCD_GRN0

LCD_RED0

BT_UART_RX0

JTAG_RST

BT_UART_RTS0

JTAG_TMS

I2C_CLK1

LCD_BLU4

TOUCH_DAT

BT_UART_TX0

LCD_GRN1

LCD_GRN5

LCD_BLU6

LCD_GRN4

LCD_DOTCLK

AUD_BCLK

LCD_RED1

LCD_HSYNC

LCD_GRN2

LCD_RED3

JTAG_TDO

LCD_BLU7

JTAG_TDI

LCD_RED5

PWR_ON_OFF

LCD_RED7

LCD_BLU1

CHG_STATUS

LCD_BLU2

LCD_GRN6

JTAG_RTCK

AUD_LRCK

LCD_RED6

BT_UART_CTS0

GND

LCD_BLU0

LCD_GRN3

I2C_DAT1

LCD_GRN7

LCD_RED4

LCD_BLU3

LCD_VSYNC

LCD_BLU5

MUTE

LED_DIMMING

AUD_DATA_OUT

AUD_DATA_IN

CPU_RST

EARPHONE_DET

R

41

3

1M

BT_WAKE

GND

P_3.0V

P_3.0V

TOUCH_CLK

TOUCH_INTR

CHARGE_EN

TOUCH_CE

RESET_IN

EXT_PWR

C

40

6

10

0n

F

R407

1K

DEVICE_DET

LCD_CLK

LCD_ENABLE

P_3.0V

LCD_DATA_OUT

LCD_DATA_IN

P_3.0V

I2C_CLK0

I2C_DAT0

GND

CLK_SELECT

CLK_SELECT

EXT_PWR

BOOT_MODE1

BOOT_MODE0

GND

P_3.0V

C

40

4

10

0n

F

GND

R

41

7

47

K

GND

VIDEO_EN

INN_BATT

GND

C403

7pF

1

2

C402

7pF

1

2

GND

X402

32.768KHz

1

IN

2

OUT

3

GND

U402

S-35392A

1 32KO

2 XOUT

3 XIN

4 VSS

5

INT2

6

SCL

7

SDA

8

VDD

32.768KHZ_OUT

P_3.0V

32.768KHZ_OUT

FM_SEARCH

BT_RST

LCD_CHECK

LCD_RST

LCD_CS

X403

24MHz

1

2

3

4

PWR_IN_CPU

BOOT_MODE1

BOOT_MODE0

JTAG_RST

GND

FM_BUS_EN

D402

KDS121V

UART_TX1

UART_RX1

NAND_CS_CTL

CORE_CTL

VOLUME-

R

40

9

10

K

GND

NAND_R/B1

NAND_R/B2

NAND_R/B3

NAND_R/B4

NAND_R/B5

NAND_R/B6

NAND_R/B7

D401

KDS121V

P_3.0V

PWR_IN_DDCON

R404

22K

I2C_DAT0

I2C_CLK0

C

40

7

0.

02

2n

F

C

40

9

0.

02

2n

F

U401

NC7SV08P5X

1 A

2 B

3

GND

4

Y

5

Vcc

LP_CTL

C

40

8

10

0n

F

R

42

1

4.

7K

R

42

4

4.

7K

R

42

5

4.

7K

R

42

2

4.

7K

R

41

0

22

BT_REG_EN

NAND_SELECT

AUD_MCLK

R411

22

BOOT_MODE0

R406

22K

R

40

8

10

0K

U301

MCIMX37

T19

PMIC_VSTBY

R16

PMIC_PWRFAIL

R19

CKIL

N18

CKIH

P15

CLK_SS

W7

WDOG_RST/PMIC_RDY/GPIO3_28

N14

RESET_IN_B

N15

POR_B

P16

BOOT_MODE0/AUD_MCLK2

P18

BOOT_MODE1

M19

XTAL

N19

EXTAL

R1

THDIODE

R18

TEST_MODE

F18

GPANAIO

H4

LCD_HSYNC/GPIO3_31

G2

LCD_VSYNC/GPIO3_29

P2

LCD_WR/GPIO3_10

P1

LCD_RD/GPIO3_11

N6

LCD_RS/GPIO3_12

N2

LCD_RDY/GPIO1_30

N5

LCD_CS/GPIO3_13

F1

LCD_DOTCLK/GPIO3_30

T8

GPIO1_31/WDOG_RST_B_DEB

R9

UART2_RXD_MUX/GPIO2_31

V8

UART2_TXD_MUX/GPIO2_30

P9

UART2_RTS_MUX/GPIO2_29

W8

UART2_CTS

W9

GPIO2_27

V9

GPIO2_26

T9

UART_TX1/GPIO2_25

V10

UART_RX1/GPIO_24

T6

CSPI2_SCLK/I2C3_SCLK/GPIO3_9

W4

CSPI2_SS1/GPIO3_8

V5

CSPI2_SS0/GPIO3_7

W5

CSPI2_MISO/GPIO3_6

R7

CSPI2_MOSI/I2C3_SDA/GPIO3_5

T7

CSPI1_SCLK/I2C1_SCL/GPIO3_4

V6

CSPI1_SS1/GPIO3_3

R8

CSPI1_SS0/GPIO3_2

W6

CSPI1_MISO/GPIO3_1

V7

CSPI1_MOSI/GPIO3_0

T4

AUD_LRCK

U2

AUD_BCLK

R6

AUD_DAI

V1

AUD_DAO

V2

GPIO2_19

T5

GPIO2_18

V3

UART3_CTS/GPIO2_17

W2

UART3_R_RTS/GPIO2_16

W3

UART3_TXD_MUX/GPIO2_15

V4

UART3_RXD_MUX/GPIO2_14

M16

I2C1_DAT/GPIO2_13

M14

I2C1_CLK/GPIO2_12

R10

GPIO1_27

W10

GPIO1_26

P10

GPIO1_25

N11

CSPI3_MISO/GPIO1_24

R11

CSPI3_SCLK/GPIO1_23

N9

CSPI3_MOSI/GPIO1_22

V18

SD1_DATA3/CSPI2_SS0/GPIO1_21

V19

SD1_DATA2/GPIO1_20

U19

SD1_DATA1/GPIO1_19

U18

SD1_DATA0/CSPI3_MIOS/GPIO1_18

T18

SD1_CLK/CSPI3_SCLK/GPIO1_17

T16

SD1_CMD/CSPI3_MOSI/GPIO1_16

H5

ETM_CTL/GPIO_D13

G5

EIM_RW/GPIO1_9

H6

ETM_CLK/GPIO_10

G4

EIM_CS1/GPIO2_1

F2

EIM_CS0/GPIO2_0

J6

DISP1_DAT23

G1

DISP1_DAT22

J5

DISP1_DAT21

H2

DISP1_DAT20

J4

DISP1_DAT19/ETM_D3

H1

DISP1_DAT18/ETM_D2

K6

DISP1_DAT17/ETM_D1

J1

DISP1_DAT16/ETM_D0

J2

DISP1_DAT15

K5

DISP1_DAT14

L6

DISP1_DAT13

K2

DISP1_DAT12

L5

DISP1_DAT11

K1

DISP1_DAT10

L4

DISP1_DAT9

L1

DISP1_DAT8

L2

DISP1_DAT7

M6

DISP1_DAT6

M5

DISP1_DAT5

M2

DISP1_DAT4

M1

DISP1_DAT3

M4

DISP1_DAT2

N4

DISP1_DAT1

N1

DISP1_DAT0

P4

GPIO1_7

P5

GPIO1_6/CLK0/AUD_MCLK

R2

GPIO1_5/USB_PWR

R4

GPIO1_4

T1

GPIO1_3

R5

GPIO1_2

T2

GPIO1_1/I2C2_SDA

U1

GPIO1_0/I2C2_SCL

P13

JTAG_MOD

T14

JTAG_DE_B

R13

JTAG_TRSTB

V16

JTAG_TDO

W16

JTAG_TDI

W17

JTAG_TMS

V17

JTAG_TCK

W18

JTAG_RTCK

LED_PWM

V

D

40

1

14

V

R

41

2

4.

7K

R401

4.7K

P3.3_CTL

R

40

5

6.

8K

R

41

5

6.

8K

R

40

2

10

K

R

40

3

4.

7K

R

42

6

47

K

R

42

3

47

K

R

42

0

47

K

RED

BLUE

GREEN

FUEL GAUGE

CPU ---> LCD

LCD ---> CPU

RTC, CODEC, FM

10 : NAND BOOT

1.10V

CKIL

BOOT MODE

REAL TIME CLOCK

SPI3 INTERFACE

TOUCH INTERFACE

CLK/DAT <--I2C_3

ARM_DEBUG

11 : USB BOOT

PWR_IN_CPU

LED_DIMMING

MUTE

PWR_ON_OFF

Default Low port

Place this part to CPU as close as possible

LCD_RESET

SRTC_POW

PER4

PER_9

PER_2

PER_9

NVCC_OSC

PER4

PER9

USBPHY

PER8

PER2

PER3

NVCC_IPU

NVCC_CNTR

PER13

PER14

NVCC_EMI

PER6

AND GATE

VIDEO_EN

RESET_IN

NAND_CS_CTL

CODEC;MCLK

POWER

TP4

TP6

TP7

TP5

TP6

TP4

TP7

TP5

Содержание YP-R1

Страница 15: ...3 4 Samsung Electronics MEMO ...

Страница 44: ...Samsung Electronics 4 29 Troubleshooting Install completed Check device manager ...

Страница 48: ...MEMO Samsung Electronics 4 33 ...

Страница 53: ...5 5 Samsung Electronics MEMO ...

Страница 55: ...6 2 Samsung Electronics PCB Diagram 6 1 1 Test Point Wave Form TP1 TP2 TP3 TP4 TP5 TP6 TP8 TP7 ...

Страница 58: ...Samsung Electronics 6 5 PCB Diagram 6 2 2 Test Point Wave Form TP2 TP3 TP4 TP7 TP6 ...

Страница 59: ...6 6 Samsung Electronics MEMO ...

Страница 69: ...7 10 Samsung Electronics MEMO ...