User’s Manual

85

The interrupts differ from most Z80 or Z180 interrupts in that the 256-byte tables pointed

to EIR and IIR contain the actual instructions beginning the interrupt routines rather than a

16-bit pointer to the routine. The interrupt vectors are spaced 16 bytes apart so that the

entire code will fit in the table for very small interrupt routines.

Interrupts have priority 1, 2 or 3. The processor operates at priority 0, 1, 2 or 3. If an inter-

rupt is being requested, and its priority is higher than the priority of the processor, the

interrupt will take place after then next instruction. The interrupt automatically raises the

processor’s priority to its own priority. The old processor priority is pushed into the 4-

position stack of priorities contained in the IP register. Multiple devices can be requesting

interrupts at the same time. In each case there is a latch set in the device that requests the

interrupt. If that latch is cleared before the interrupt is latched by the central interrupt

logic, then the interrupt request is lost and no interrupt takes place. This is shown in

Table 7-12. The priorities shown in this table apply only for interrupts of the same priority

level and are only meaningful if two interrupts are requested at the same time. Most of the

devices can be programmed to interrupt at priority level 1, 2 or 3.

In the case of the external interrupts the only action that will clear the interrupt request is

for the interrupt to take place, which automatically clears the request. A special action

must be taken in the interrupt service routine for the other interrupts.

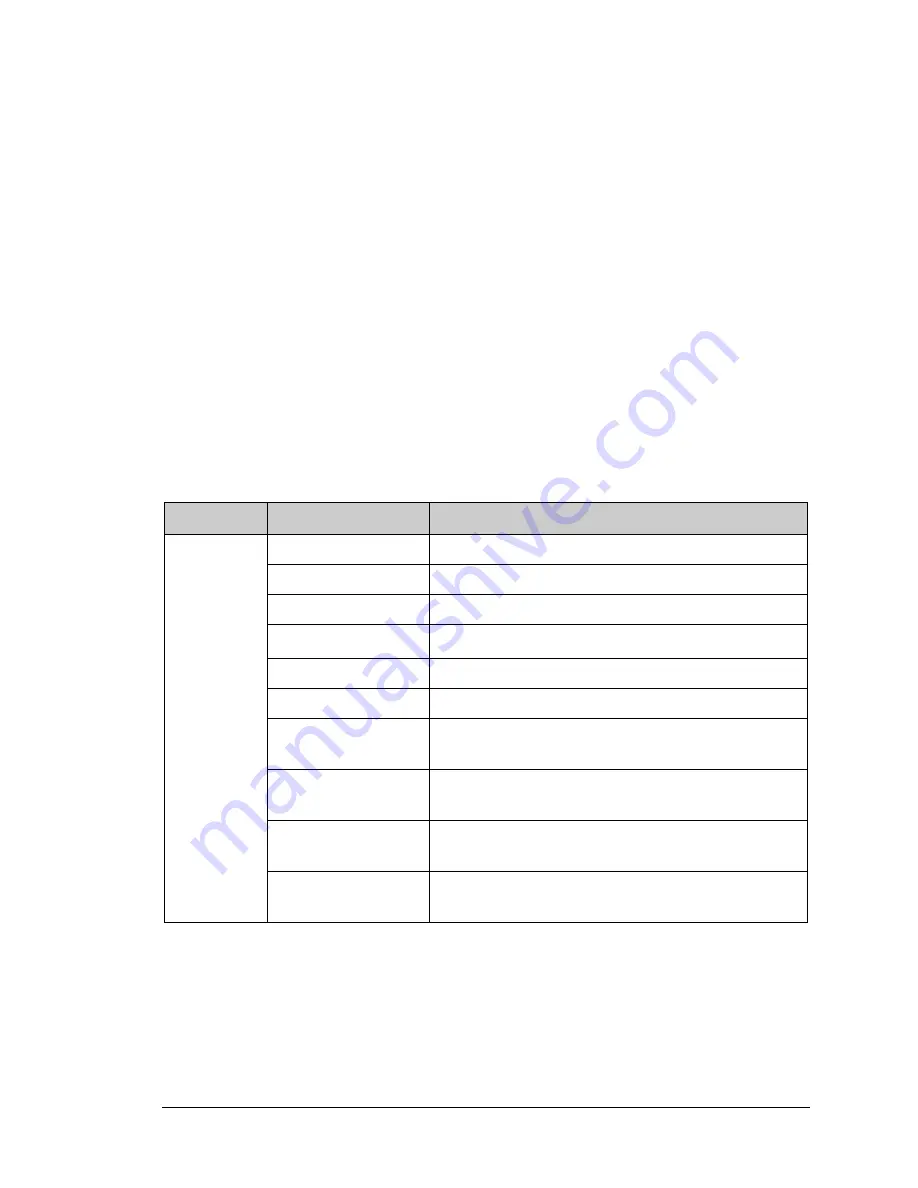

Table 7-12. Interrupts—Priority and Action to Clear Requests

Priority

Interrupt Source

Action Required to Clear the Interrupt

Highest

External 1

Automatically by interrupt acknowledge.

External 0

Automatically by interrupt acknowledge.

Periodic (2 kHz)

Read GCSR.

Timer B

Read TBCSR

*

.

* If the compare registers (TBMxR and TBLxR) are not written within the ISR, the interrupt will

will only be requested once.

Timer A

Read TACSR.

Slave Port

Write SPSR.

Serial Port A

Rx: Read SADR or SAAR.

Tx: Write SADR, SAAR or SASR

Serial Port B

Rx: Read SBDR or SBAR.

Tx: Write SBDR, SBAR or SBSR

Serial Port C

Rx: Read SCDR or SCAR.

Tx: Write SCDR, SCAR or SCSR

Lowest

Serial Port D

Rx: Read SDDR or SDAR.

Tx: Write SDDR, SDAR or SDSR

Содержание 2000

Страница 1: ...Rabbit 2000 Microprocessor User s Manual 019 0069 041018 M...

Страница 12: ...6 Rabbit 2000 Microprocessor...

Страница 46: ...40 Rabbit 2000 Microprocessor...

Страница 54: ...48 Rabbit 2000 Microprocessor...

Страница 76: ...70 Rabbit 2000 Microprocessor...

Страница 96: ...90 Rabbit 2000 Microprocessor...

Страница 142: ...136 Rabbit 2000 Microprocessor...

Страница 154: ...148 Rabbit 2000 Microprocessor...

Страница 170: ...164 Rabbit 2000 Microprocessor...

Страница 174: ...168 Rabbit 2000 Microprocessor...

Страница 180: ...174 Rabbit 2000 Microprocessor...

Страница 202: ...196 Rabbit 2000 Microprocessor...

Страница 206: ...200 Rabbit 2000 Microprocessor...

Страница 226: ......

Страница 230: ...224 Rabbit 2000 Microprocessor...