Instruction Reference Manual

103

Description

Logically shifts to the right the bits in the register r (any of the registers A, B, C, D, E, H, or L). Each bit is

shifted to the next lowest-order bit position (Bit 7 shifts to bit 6, etc.) Bit 0 shift to the Carry Flag, CF. Bit 7 is

reset. See Figure 7 on page 102.

SRL r

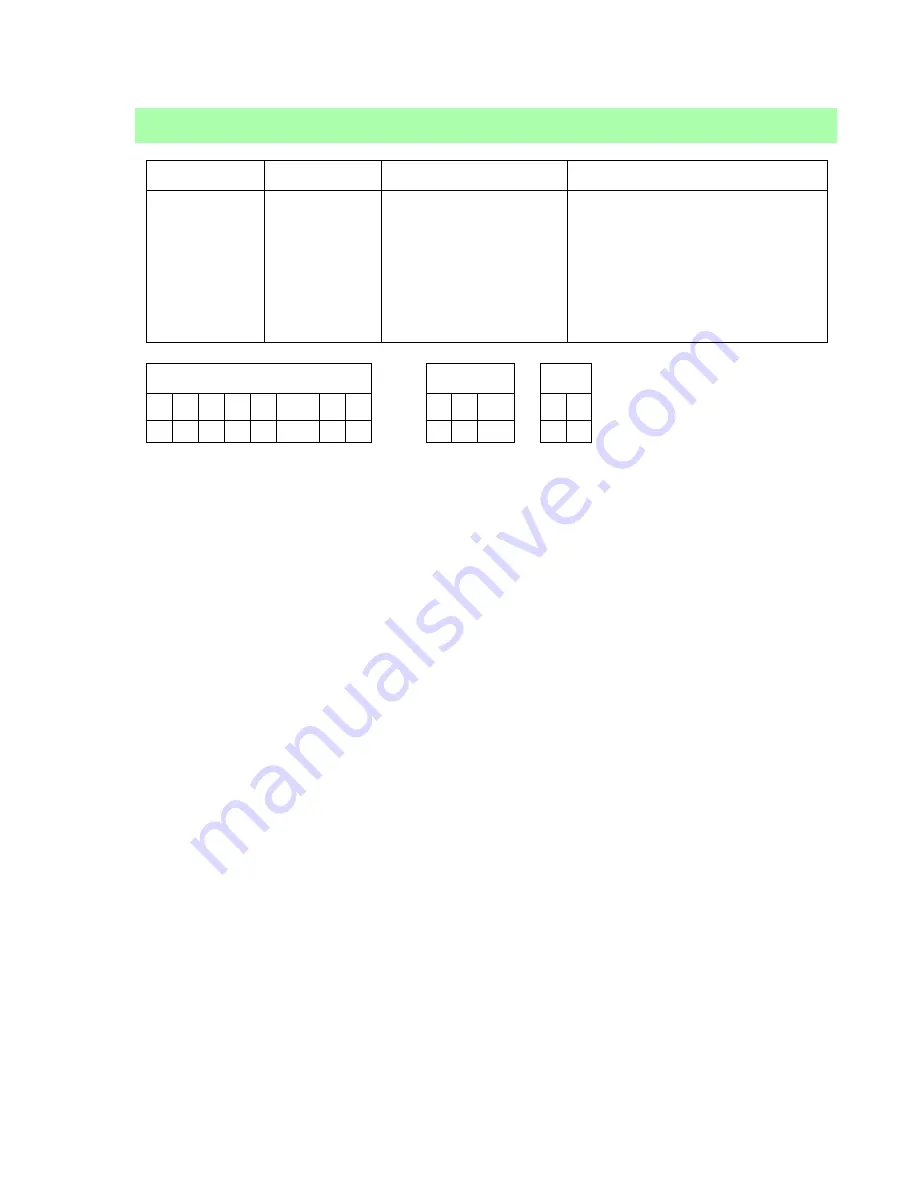

Opcode

Instruction

Clocks

Operation

——

CB 3F

CB 38

CB 39

CB 3A

CB 3B

CB 3C

CB 3D

SRL r

SRL A

SRL B

SRL C

SRL D

SRL E

SRL H

SRL L

4 (2,2)

4 (2,2)

4 (2,2)

4 (2,2)

4 (2,2)

4 (2,2)

4 (2,2)

4 (2,2)

r = {0,r[7,1]}; CF = r[0]

A = {0,A[7,1]}; CF = A[0]

B = {0,B[7,1]}; CF = B[0]

C = {0,C[7,1]}; CF = C[0]

D = {0,D[7,1]}; CF = D[0]

E = {0,E[7,1]}; CF = E[0]

H = {0,H[7,1]}; CF = H[0]

L = {0,L[7,1]}; CF = L[0]

Flags

ALTD

I/O

S

Z

L/V

C

F

R

SP

S

D

•

•

L

•

•

•

Содержание 2000

Страница 2: ...ii Rabbit 2000 3000 Microprocessor...

Страница 4: ...iv Rabbit 2000 Microprocessor...

Страница 16: ...12 Rabbit 2000 3000 Microprocessor...

Страница 112: ...108 Rabbit 2000 3000 Microprocessor...

Страница 120: ...ii Rabbit 2000 3000 Microprocessor...