EN 146

3139 785 31150

9.

Circuit- and IC Description

SAA7117A

7007

CHRYSALIS

PNX7100EH

7400

SDRAM

HDD

7812

133MHz

SDRAM

7813

1394 LINK

7201

AUDIO PLL

7300

1394 PHY

24.576 MHz

24.576 MHz

7200

4 MHz

BASIC

ENGINE

IDE1

IDE2

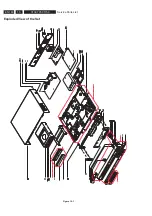

Figure 9-5 Clock Distribution

The Chrysalis chip has a complex system, which is needed to

support the processes running at different frequencies such

as video decoding, audio decoding or peripheral I/O devices

etc. To ensure a synchronous initialization of all the registers

and state machines, all the PLLs are switched to their default

frequency and the reset sequence is run at 4MHz.

Then when the booting control unit is correctly initialized and

once it has captured all the booting parameters, it sets the

PLLs to its functional frequencies to allow the modules to

run at their nominal frequencies. Thanks to a clock blocking

mechanism, the frequency switching is glitch free.

System clocks:

•

PNX7100EH (7400, pin AF9 and AF10) : 4MHz provided

by the x’tal 7402

•

SAA7117A (7007, pins A3 and B4) : 24.576MHz provided

by x’tal 1001

•

1394-PHY (7200, pins 59 and 60) : 24.576MHz provided

by x’tal 1201

•

1394-LINK (7201, pin 88) : 49.152MHz provided by

1394-PHY

•

SDRAM (7812 and 7813, pin 38) : 133MHz provided by

the

Chrysalis

chip

Video

Part

The analogue video input signals CVBS, YC and RGB

are routed via the board to connector 1904 and sent to

Video Input Processor, SAA7117A [7007]. The Video Input

Processor encodes the analogue video to digital video stream

(CCIR656 format). The output stream, named ITU_IN(7:0),

is then routed to the Chrysalis chip. This IC encodes and

decodes the digital video stream into / from MPEG2 format.

The digital video input signals from the DV-in are routed from

connector 1204 via the 1394 PHY IC [7200] and the 1394

LINK IC [7201] also to the Chrysalis chip.

Audio

Part

I

2

S audio is sent from the Analog board to the Chrysalis chip

via connector 1900.

The Chrysalis chip compresses the I

2

S audio data into an

MPEG1-L2 / AC3 audio stream.

Front-end I

2

S

The Chrysalis chip interfaces directly to the Basic Engine and

HDD via the IDE connectors.

It buffers the data streams that are coming from (or going to)

these hardware devices.

In the Chrysalis chip, the video MPEG2 stream and the audio

AC3 stream are multiplexed into an I

2

S stream. In normal

recording the serial data are send to the HDD for recording.

Only archiving and playback is done with optical drive.

9.5.2. Playback

mode

During playback, the serial data from the Basic Engine is

going directly to the Chrysalis chip via ATAPI interface. The

Chrysalis chip has the following outputs:

•

Analog video CVBS, YC and RGB outputs on

connector

1904

•

I

2

S audio (PCM format) on connector 1900

•

SPDIF audio (digital audio output) on connector 1900

•

Progressive Scan output connector 1002 (Not for

European

version)

9.5.3. Basic

Engine

Interface

The Digital board is equipped with 2 IDE bus (ATAPI) for

connecting to the Basic Engine and HDD via connectors 1102

and 1107 respectively.

9.5.4. Clock

Distribution

Содержание DVDR3330H/02

Страница 102: ...EN 102 3139 785 31150 Firmware Upgrading Diagnostic Software 5 Notes ...

Страница 138: ...EN 138 3139 785 31150 7 Circuit Diagrams and PWB Layouts Notes ...

Страница 156: ...EN 156 3139 785 31150 9 Circuit and IC Description PIN DESCRIPTION AND CONFIGURATION ...

Страница 160: ...EN 160 3139 785 31150 910 901 910 910 Exploded View of the Set Figure 10 1 10 Service Parts List ...