IC Data Sheets

8.

Figure 8-2 Internal pin configuration [1/2]

19620_301_140111.eps

140111

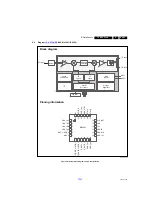

Pinning Information

MT5561LVNT

3

32

2

9

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

9

9

1

10

A

A

DVSS

AO0P

AOCKP

AE1P

DVSS

CI_A3

B

B

GPIO0

AO0N

AOCKN

AE1N

CI_D0

CI_REG#

C

C

TCON4

TCON2

AO1P

AO2P

AO3P

AE0P

AE2P

AE3P

CI_A1

CI_MOVAL

D

D

TCON5

TCON7

AO1N

AO2N

AO3N

AE0N

AE2N

AE3N

CI_A0

CI_A4

E

E

TCON3

TCON0

GPIO1

OPWM0

CI_MDO1

CI_MDO2

CI_A12

CI_A5

F

F

TCON8

TCON1

TCON6

OSCL1

OSDA1

DVSS

CI_CD2#

CI_D2

CI_A2

G

G

PDD6

PDD0

PDD3

PDD1

OPWM1

OPWM2

DVSS

DVSS

H

H

PDD4

GPIO4

GPIO3

DVSS

DVSS

JJ

POOE

#

POCE1#

PDD7

POCE0#

POWE#

PDD5

DVSS

VCCK

DVSS

K

K

PACLE

PAALE

PDD2

PARB#

VCCK

VCCK

VCCK

VCCK

DVSS

DVSS

L

L

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

DVSS

DVSS

M

M

DVSS

DVSS

DVSS

DVSS

DVSS

DVSS

VCCK

VCCK

DVSS

DVSS

N

N

DDRV

DDRV

DDRV

DDRV

DDRV

DDRV

DVSS

DVSS

DVSS

VCC3IO

P

P

DDRV

REF

ZQ

AOLRC

K

OSDA0

DVSS

ADIN1

VCC3IO

VCC3IO

R

R

AOBC

K

AOMCLK

AOSDAT

A0

ASPDIF

O

OSCL0

DVSS

ADIN7

AVDD33_E

TH

AVDD33_HD

MI

T

T

OPWRSB

OIRI

AOSDAT

A1

DVSS

ADIN6

ADIN0

ADIN4

U

U

U0TX

U0RX

OPCTRL

0

OPCTRL

4

ADIN5

ADIN3

HDMI_0_SCL

ADIN2

HDMI_0_R

X_1B

HSYNC

V

V

OPCT

RL3

OPCTRL1

OPCTRL

2

VGA_SD

A

VGA_SCL

HDMI_0_S

DA

HDMI_0_RX_

0B

HDMI_0_RX_0

HDMI_0_R

X_1

VSYNC

W

W

RXVN

RXVP

REXT_E

TH

HDMI_0_HPD

HDMI_0_RX_

CB

HDMI_0_R

X_2B

ORESETB

Y

Y

TXVN

TXVP

DVSS

AVDD12

_ETH

AVDD12_HDM

I_0

HDMI_0_RX_

C

HDMI_0_R

X_2

AVDD10_LD

O

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

9

9

1

10