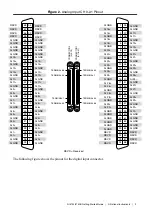

Figure 4.

NI 5752 Block Diagram

I16

AI B8

AI B15

I16

I16

I16

AI C16

AI C23

I16

AI D24

AI D31

ForceInit

cSpiDevice

cSpiAddr

cSpiWrData

cSpiRxData

cSpiReadEn

cSpiWriteEn

I16

I16

I16

AI A0

AI A7

Analog

Connectors

Digital

Connector

Exter

nal

Cloc

k In

NI 5752 Adapter Module

LabVIEW FPGA CLIP

Clock

Multiplexer

Deserializer

Deserializer

Deserializer

Deserializer

Data Clock

DI 0

DI 1

DO 0

AdcTgcStart

AdcRegisterReset

SampleClkSrcSelect

Sync Clock

(DSTARA)

50 MHz Internal

Oscillator

ADC

A

ADC

B

ADC

C

ADC

D

ADC

Control

SPI

Engine

(AI 0+, AI 0–) ... (AI 7+, AI 7–)

(AI 8+, AI 8–) ... (AI 15+, AI 15–)

(AI 16+, AI 16–) ... (AI 23+, AI 23–)

(AI 24+, AI 24–) ... (AI 31+, AI 31–)

InitDone

PllUnlocked

ADCErrorA

ADCErrorB

ADCErrorC

ADCErrorD

DO 15

Div Bit Clock

DI 0

X 3

NI 5752/5752B Getting Started Guide

|

© National Instruments

|

11