User’s Manual U12978EJ3V0UD

6

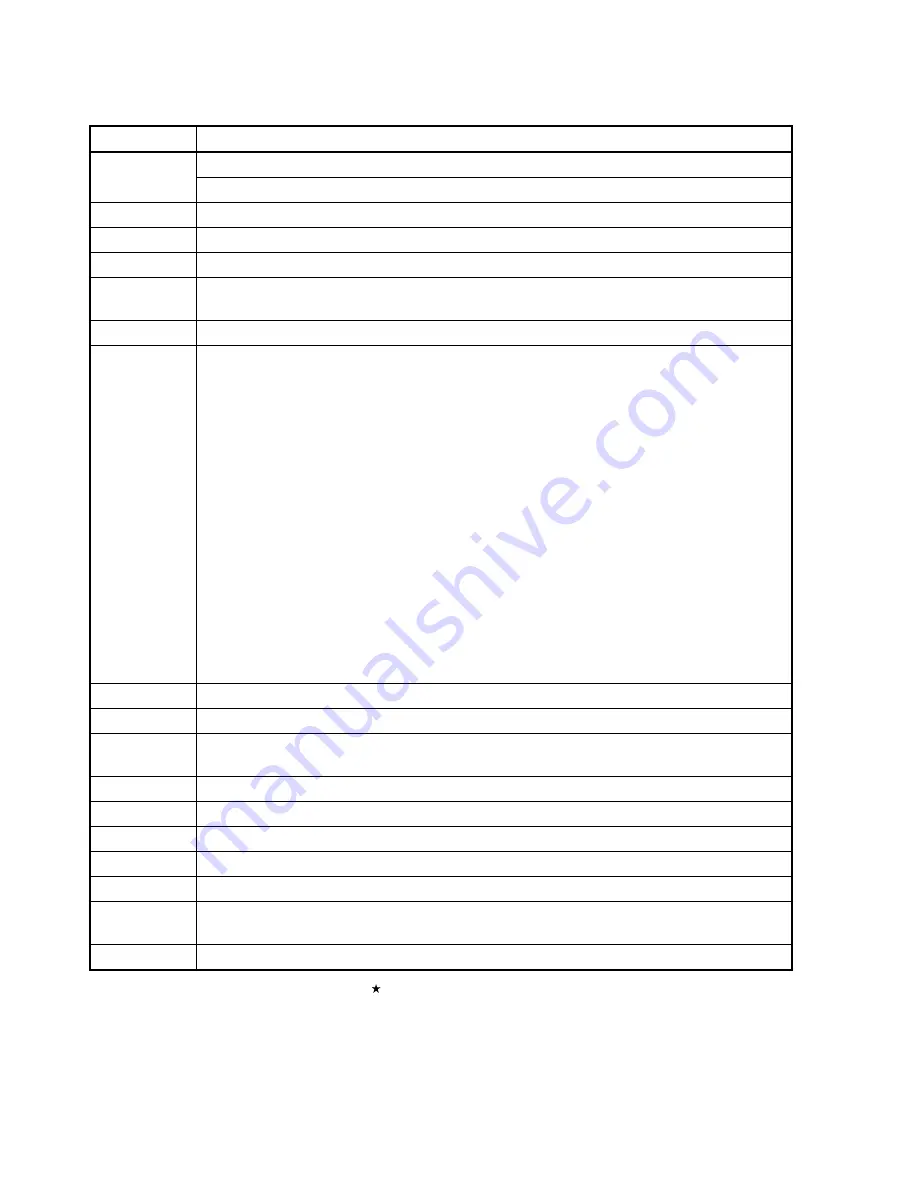

Major Revisions in This Edition

Page

Contents

Deletion of CU-type and GB-3BS type packages

Throughout

Deletion of indication “under development” for

µ

PD78F9801

p. 21

Modification of operating ambient temperature when flash memory is written in

1.1 Features

p. 27

Addition of outline of timer in

1.7 Functions

pp. 29, 31 to 33

Modification of handling of REGC and V

PP

pins

pp. 35, 36

Correction of address values in

Figure 3-1 Memory Map (

µµµµ

PD789800)

and

Figure 3-2 Memory Map

(

µµµµ

PD78F9801)

p. 75

Modification of

Figure 5-3 External Circuit of System Clock Oscillator (b) External clock

pp. 98, 103,

105, 106,

108 to 112,

115 to 117, 120,

125, 127 to 130

CHAPTER 8 USB FUNCTION

•

Modification of chapter composition

•

Standardization of buffer name indications as receive token bank, receive data bank, and transmit data

banks 0 and 1

•

Addition of image diagrams for reception and transmission

•

Addition of register value for SETUP reception

•

Modification of description on data handshake packet receive mode register (URXMOD)

•

Addition of description on packet receive status register (RXSTAT) and modification of read-only bit

•

Addition of

Note

for token packet receive result store register (TRXRSL)

•

Addition of

Caution

for data packet transmit reservation register (DTXRSV)

•

Modification of description of bit 1 (DNAEN) of handshake packet transmit reservation register (HTXRSV)

•

Change of contents of

8.5.2 Remote wakeup control operation

•

Addition of

Table 8-4 List of Sources of Interrupts from USB Function

•

Correction of incorrect flag name in

8.6 Interrupt Request from USB Function

•

Addition of description on USB reset/Resume detection interrupt (INTUSBRE)

•

Addition of

8.7 USB Function Control

p. 162

Modification of

Figure 10-1 Block Diagram of Regulator and USB Driver/Receiver

and

Cautions

p. 164

Addition of

Remark

in

Table 11-1 Interrupt Source List

p. 167

Addition of

Caution 3

on watchdog timer interrupt to

Figure 11-2 Format of Interrupt Request Flag

Register

p. 184

Addition of

12.2.2 STOP mode (3) Cautions on STOP instruction execution

pp. 191 to 199

Revision of contents of flash memory programming as

14.1 Flash Memory Characteristics

pp. 210 to 218

Addition of

CHAPTER 16 ELECTRICAL SPECIFICATIONS

p. 219

Addition of

CHAPTER 17 PACKAGE DRAWING

p. 220

Addition of

CHAPTER 18 RECOMMENDED SOLDERING CONDITIONS

pp. 221 to 228

Revision of

APPENDIX A DEVELOPMENT TOOLS

Deletion of embedded software and addition of notes on target system design

pp. 233, 234

Addition of the revision contents in 3rd edition in

APPENDIX C REVISION HISTORY

The mark shows major revised points.

Содержание switch

Страница 2: ...User s Manual U12978EJ3V0UD 2 MEMO ...