© National Instruments

|

4-7

NI cDAQ-9181/9184/9188/9191 User Manual

In NI-DAQmx, the filter is programmed by setting the minimum pulse width,

Tp

1

, that will pass

the filter, and is selectable in 25 ns increments. The appropriate Filter Clock is selected by the

driver. Pulses of length less than 1/2

Tp

will be rejected, and the filtering behavior of lengths

between 1/2

Tp

and 1

Tp

are not defined because they depend on the phase of the Filter Clock

relative to the input signal.

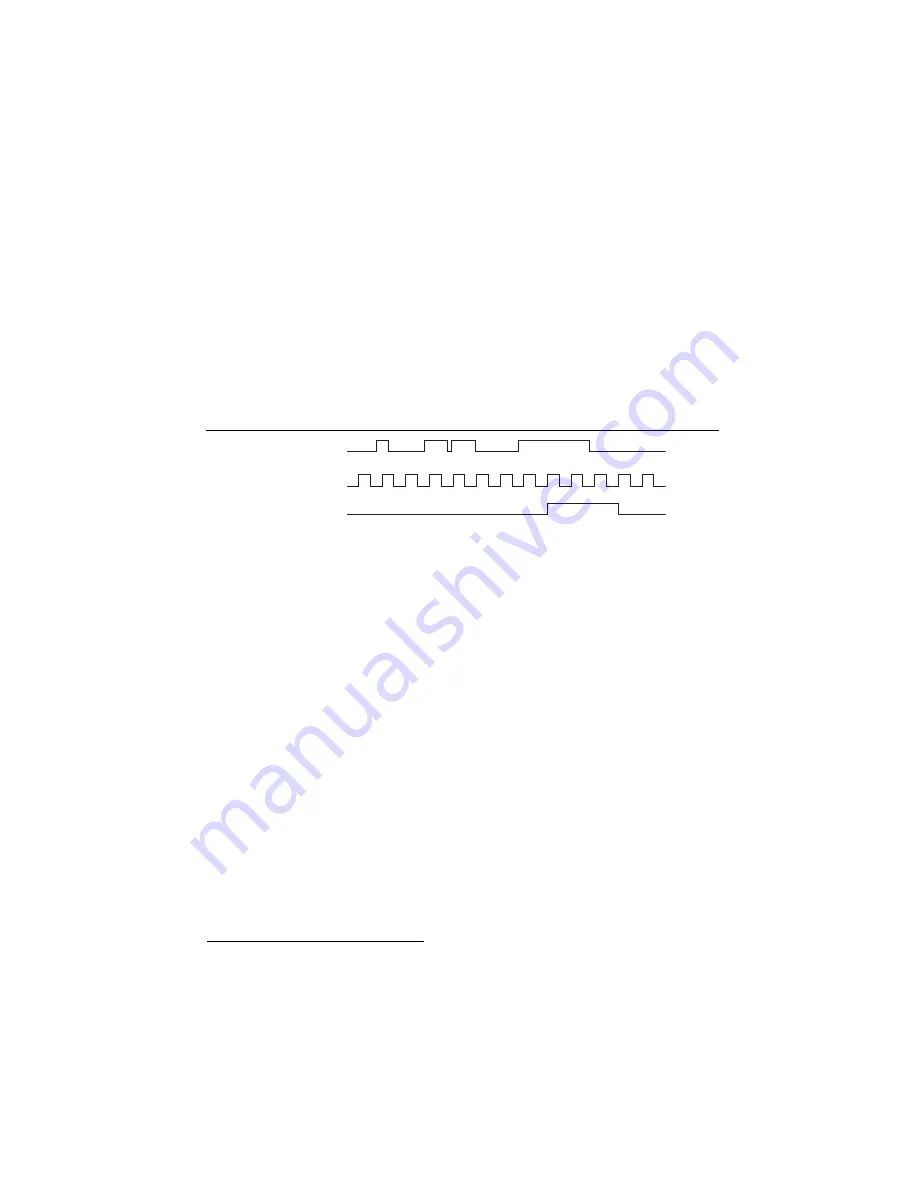

Figure 4-3 shows an example of low-to-high transitions of the input signal. High-to-low

transitions work similarly.

Assume that an input terminal has been low for a long time. The input terminal then changes

from low to high, but glitches several times. When the filter clock has sampled the signal high

on consecutive rising edges, the low-to-high transition is propagated to the rest of the circuit.

Figure 4-3.

Filter Example

Getting Started with DI Applications in Software

You can use the cDAQ chassis in the following digital input applications:

•

Single-point acquisition

•

Finite acquisition

•

Continuous acquisition

For more information about programming digital input applications and triggers in software,

refer to the

NI-DAQmx Help

or the

LabVIEW Help

for more information.

Change Detection Event

The Change Detection Event is the signal generated when a change on the rising or falling edge

lines is detected by the change detection task.

Routing Change Detection Event to an Output Terminal

You can route ChangeDetectionEvent to any output PFI terminal.

Change Detection Acquisition

You can configure lines on parallel digital modules to detect rising or falling edges. When one

or more of these lines sees the edge specified for that line, the cDAQ chassis samples all the lines

in the task. The rising and falling edge lines do not necessarily have to be in the task.

1

Tp

is a nominal value; the accuracy of the chassis timebase and I/O distortion will affect this value.

Digit

a

l Inp

u

t P0.

x

Filter Clock

Filtered Inp

u

t

1

1

2

1

1

2

1